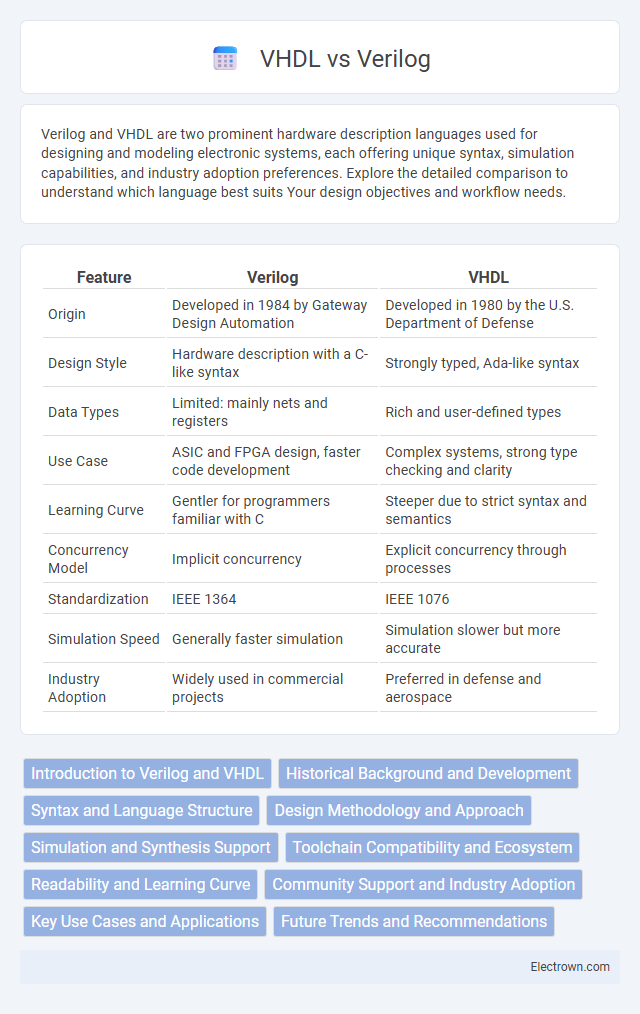

Verilog and VHDL are two prominent hardware description languages used for designing and modeling electronic systems, each offering unique syntax, simulation capabilities, and industry adoption preferences. Explore the detailed comparison to understand which language best suits Your design objectives and workflow needs.

Table of Comparison

| Feature | Verilog | VHDL |

|---|---|---|

| Origin | Developed in 1984 by Gateway Design Automation | Developed in 1980 by the U.S. Department of Defense |

| Design Style | Hardware description with a C-like syntax | Strongly typed, Ada-like syntax |

| Data Types | Limited: mainly nets and registers | Rich and user-defined types |

| Use Case | ASIC and FPGA design, faster code development | Complex systems, strong type checking and clarity |

| Learning Curve | Gentler for programmers familiar with C | Steeper due to strict syntax and semantics |

| Concurrency Model | Implicit concurrency | Explicit concurrency through processes |

| Standardization | IEEE 1364 | IEEE 1076 |

| Simulation Speed | Generally faster simulation | Simulation slower but more accurate |

| Industry Adoption | Widely used in commercial projects | Preferred in defense and aerospace |

Introduction to Verilog and VHDL

Verilog and VHDL are hardware description languages used for designing and modeling digital circuits, essential in FPGA and ASIC development. Verilog offers a syntax similar to C programming, making it popular for rapid prototyping and system design. VHDL provides strong typing and extensive concurrency features, preferred for complex designs requiring rigorous verification and documentation.

Historical Background and Development

Verilog, developed in the mid-1980s by Gateway Design Automation, was designed for hardware description and quickly gained popularity due to its C-like syntax and ease of use in digital circuit modeling. VHDL, originating from the 1980s as part of a U.S. Department of Defense project, was created to document and simulate electronic systems with a strong emphasis on hardware design verification. Your choice between Verilog and VHDL can depend on legacy system requirements, industry adoption, and specific project needs linked to their distinct historical roots and development paths.

Syntax and Language Structure

Verilog features a C-like syntax, making it more accessible to engineers familiar with programming languages such as C and C++, while VHDL adopts an Ada-like syntax that is more verbose and strongly typed, offering rigorous type checking. The language structure in Verilog emphasizes simplicity and conciseness, whereas VHDL focuses on explicitness and modular design through entities and architectures, enhancing readability and maintainability for complex systems. Choosing between them depends on Your preference for either a flexible, easier-to-learn syntax (Verilog) or a more robust, strongly-typed environment (VHDL) for hardware description.

Design Methodology and Approach

Verilog adopts a procedural design methodology resembling C programming, emphasizing concise coding and hardware description through behavioral constructs, which accelerates simulation and synthesis for digital circuits. VHDL employs a strongly typed, declarative approach with extensive use of concurrent statements and packages, enabling precise modeling of complex systems and fostering design modularity. The choice between Verilog's hardware-centric style and VHDL's rigorous abstraction affects code readability, reuse, and verification strategies in FPGA and ASIC development workflows.

Simulation and Synthesis Support

Verilog offers extensive simulation and synthesis support widely favored in ASIC and FPGA design due to its concise syntax and compatibility with many EDA tools. VHDL provides strong, robust simulation capabilities with comprehensive type checking, making it ideal for complex hardware descriptions and formal verification. Your choice depends on the preferred design flow, where Verilog excels in synthesis speed and VHDL ensures rigorous simulation accuracy.

Toolchain Compatibility and Ecosystem

Verilog offers broad toolchain compatibility with many industry-standard simulators and synthesis tools, making it a preferred choice for ASIC and FPGA design flows. VHDL benefits from a robust ecosystem supported by formal verification tools and comprehensive FPGA vendor libraries, enhancing design reliability and reusability. Your choice should consider the preferred toolchain and ecosystem support to ensure seamless integration and efficient project development.

Readability and Learning Curve

Verilog offers a syntax similar to the C programming language, making it more approachable for designers with software backgrounds and enhancing initial readability. VHDL's verbose and strongly typed nature enforces rigorous design practices but results in a steeper learning curve and more complex code understanding. Consequently, Verilog is often preferred for rapid prototyping, while VHDL excels in projects demanding high reliability and maintainability through precise documentation.

Community Support and Industry Adoption

Verilog boasts extensive community support with a large user base, numerous open-source libraries, and active forums, making it a popular choice among engineers and students. VHDL is widely adopted in aerospace and defense industries due to its strong typing and reliability features, supported by robust vendor tools and government standards. While Verilog dominates commercial semiconductor design and ASIC development, VHDL remains preferred for mission-critical FPGA applications in industries requiring high assurance.

Key Use Cases and Applications

Verilog is predominantly used in ASIC and FPGA design for digital circuit modeling, favored for its simplicity and ease in hardware description language (HDL) based synthesis and simulation in industry-standard tools. VHDL excels in highly complex and safety-critical applications such as aerospace, defense, and automotive industries, offering strong typing and better support for complex system modeling and verification. Both languages support system-level design and hardware verification, with Verilog often chosen for rapid prototyping and VHDL for rigorous, formal verification environments.

Future Trends and Recommendations

Verilog continues to gain popularity in high-speed digital design due to its simplicity and widespread industry support, while VHDL remains favored for complex, safety-critical systems requiring strong typing and robust error checking. Emerging trends highlight the integration of high-level synthesis tools that convert C++ or SystemC code into hardware descriptions, influencing both Verilog and VHDL usage. Your choice should consider project requirements and industry adoption, with Verilog preferred for rapid prototyping and VHDL recommended for long-term maintainability in aerospace or defense applications.

Verilog vs VHDL Infographic

electrown.com

electrown.com