Emitter-coupled logic (ECL) offers faster switching speeds and lower propagation delay compared to CMOS logic, making it ideal for high-frequency applications despite higher power consumption. Understanding these differences can help you choose the best logic family for your design needs; explore the rest of the article to learn more about their advantages and applications.

Table of Comparison

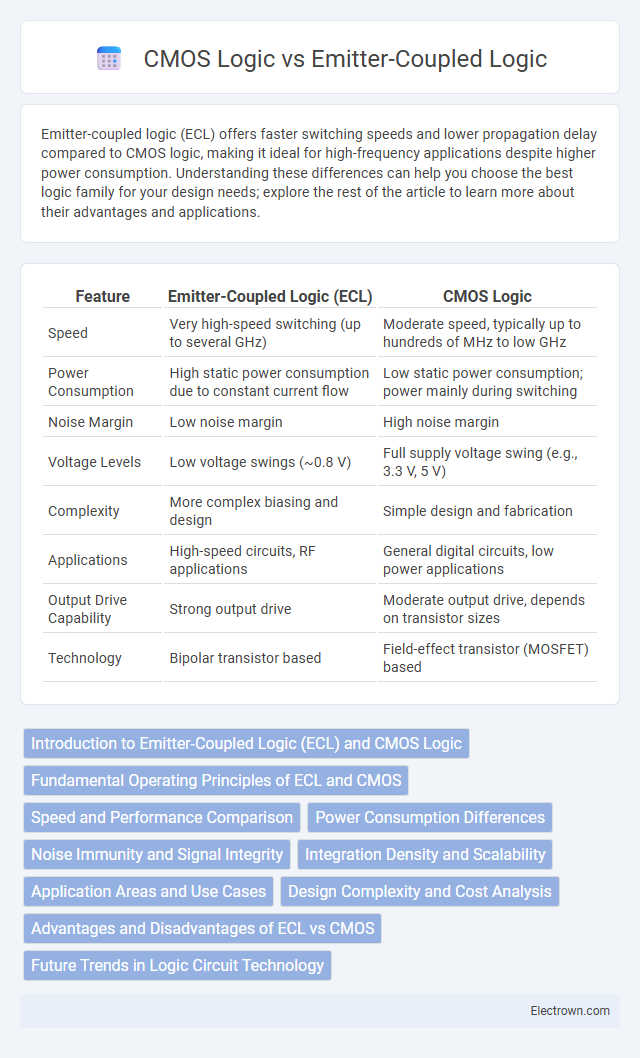

| Feature | Emitter-Coupled Logic (ECL) | CMOS Logic |

|---|---|---|

| Speed | Very high-speed switching (up to several GHz) | Moderate speed, typically up to hundreds of MHz to low GHz |

| Power Consumption | High static power consumption due to constant current flow | Low static power consumption; power mainly during switching |

| Noise Margin | Low noise margin | High noise margin |

| Voltage Levels | Low voltage swings (~0.8 V) | Full supply voltage swing (e.g., 3.3 V, 5 V) |

| Complexity | More complex biasing and design | Simple design and fabrication |

| Applications | High-speed circuits, RF applications | General digital circuits, low power applications |

| Output Drive Capability | Strong output drive | Moderate output drive, depends on transistor sizes |

| Technology | Bipolar transistor based | Field-effect transistor (MOSFET) based |

Introduction to Emitter-Coupled Logic (ECL) and CMOS Logic

Emitter-Coupled Logic (ECL) is a high-speed digital logic family that uses differential amplifier stages to achieve fast switching times by avoiding transistor saturation. CMOS logic, based on complementary pairs of p-type and n-type MOSFETs, is widely favored for its low power consumption and high noise immunity in complex integrated circuits. Your choice between ECL and CMOS depends on the trade-off between speed requirements and power efficiency in electronic design applications.

Fundamental Operating Principles of ECL and CMOS

Emitter-Coupled Logic (ECL) operates by steering current through differential pairs of transistors to achieve high-speed switching with low voltage swings, which minimizes propagation delay. Complementary Metal-Oxide-Semiconductor (CMOS) technology uses complementary pairs of p-type and n-type MOSFETs to switch between supply voltage and ground, resulting in low static power consumption and high noise immunity. ECL's constant current approach enables faster transitions, whereas CMOS relies on charging and discharging of load capacitances, significantly affecting power efficiency and speed.

Speed and Performance Comparison

Emitter-coupled logic (ECL) achieves higher switching speeds than CMOS logic due to its current-steering operation and non-saturating transistor design, enabling propagation delays as low as a few picoseconds. CMOS logic, while slower with typical delays in the nanosecond range, excels in power efficiency and integration density, making it ideal for large-scale digital circuits. ECL's superior speed and low noise margin are essential for high-frequency applications like telecommunications, whereas CMOS dominates general-purpose computing due to its scalability and low static power consumption.

Power Consumption Differences

Emitter-coupled logic (ECL) consumes significantly more power than CMOS logic because ECL uses a constant current flow, resulting in continuous power dissipation even when not switching. CMOS logic leverages complementary transistor pairs that draw power primarily during state transitions, leading to much lower dynamic and static power consumption. Your choice between ECL and CMOS will impact energy efficiency, especially in applications where power savings are critical.

Noise Immunity and Signal Integrity

Emitter-coupled logic (ECL) offers superior noise immunity due to its differential signaling and constant current operation, which minimizes voltage swings and reduces susceptibility to noise-induced errors. CMOS logic, while having lower power consumption, typically exhibits higher noise margins but can suffer from slower transition times affecting signal integrity under high-frequency conditions. ECL's faster switching speeds and low voltage noise make it ideal for high-speed, high-frequency applications where maintaining signal integrity is critical.

Integration Density and Scalability

Emitter-coupled logic (ECL) offers lower integration density compared to CMOS logic due to its larger transistor sizes and higher power dissipation, limiting scalability in complex circuits. CMOS logic achieves higher integration density with smaller transistor geometries and reduced power consumption, enabling more compact and scalable designs. Your choice between ECL and CMOS directly impacts the feasibility of large-scale, high-density integrated circuits.

Application Areas and Use Cases

Emitter-coupled logic (ECL) is extensively used in high-speed computing applications such as supercomputers, telecommunications, and radar systems due to its rapid switching capabilities and low propagation delay. CMOS logic dominates in digital integrated circuits for consumer electronics, including smartphones, microcontrollers, and memory devices, because of its low power consumption and high integration density. ECL is preferred in environments where speed is critical despite higher power usage, whereas CMOS is ideal for battery-powered and large-scale integration applications requiring energy efficiency.

Design Complexity and Cost Analysis

Emitter-coupled logic (ECL) circuits exhibit higher design complexity due to their differential amplifier configurations and constant current biasing, requiring precise transistor matching and careful layout to minimize noise and signal distortion. CMOS logic benefits from simpler design procedures, leveraging complementary MOS transistors with lower static power consumption and straightforward interconnect schemes, resulting in reduced manufacturing complexity and cost. Your choice between ECL and CMOS impacts overall cost efficiency, as ECL's specialized fabrication processes and higher power dissipation increase expenses compared to the widespread, lower-cost CMOS technology.

Advantages and Disadvantages of ECL vs CMOS

Emitter-coupled logic (ECL) offers significantly faster switching speeds and lower propagation delay compared to CMOS logic due to its differential amplifier-based design and constant current operation. However, ECL consumes much higher power and generates more heat, making it less energy-efficient than CMOS, which excels in low power consumption and high integration density. ECL's high speed suits microwave and high-frequency applications, while CMOS dominates in battery-powered and large-scale digital circuits because of its scalability and low static power dissipation.

Future Trends in Logic Circuit Technology

Emitter-coupled logic (ECL) offers ultra-high-speed switching suitable for high-frequency applications, but its power consumption limits scalability compared to CMOS logic. CMOS technology continues to dominate with advancing nanoscale fabrication, enabling lower power consumption and higher integration density, fueling innovations in AI processors and IoT devices. Future trends emphasize hybrid approaches and emerging materials like graphene to enhance speed while minimizing energy use, bridging the gap between ECL's speed and CMOS's efficiency.

Emitter-coupled logic vs CMOS logic Infographic

electrown.com

electrown.com