The Interrupt Vector Table (IVT) organizes addresses of Interrupt Service Routines (ISRs) to ensure your system responds swiftly to hardware or software interrupts. Explore the rest of this article to understand how IVTs and ISRs work together to enhance system performance.

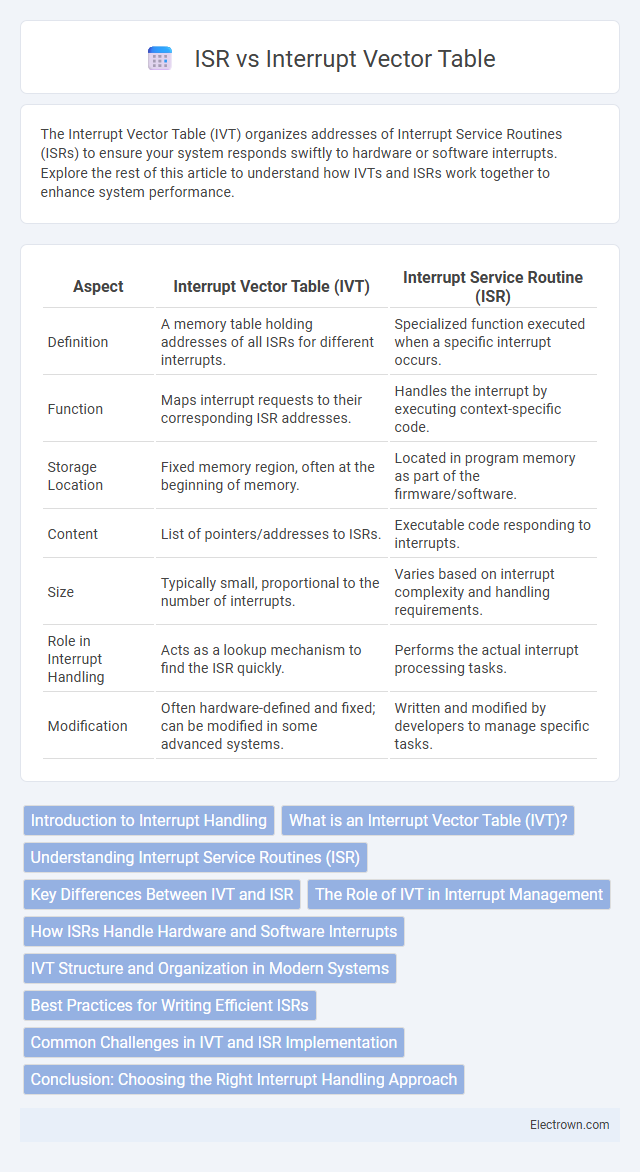

Table of Comparison

| Aspect | Interrupt Vector Table (IVT) | Interrupt Service Routine (ISR) |

|---|---|---|

| Definition | A memory table holding addresses of all ISRs for different interrupts. | Specialized function executed when a specific interrupt occurs. |

| Function | Maps interrupt requests to their corresponding ISR addresses. | Handles the interrupt by executing context-specific code. |

| Storage Location | Fixed memory region, often at the beginning of memory. | Located in program memory as part of the firmware/software. |

| Content | List of pointers/addresses to ISRs. | Executable code responding to interrupts. |

| Size | Typically small, proportional to the number of interrupts. | Varies based on interrupt complexity and handling requirements. |

| Role in Interrupt Handling | Acts as a lookup mechanism to find the ISR quickly. | Performs the actual interrupt processing tasks. |

| Modification | Often hardware-defined and fixed; can be modified in some advanced systems. | Written and modified by developers to manage specific tasks. |

Introduction to Interrupt Handling

The Interrupt Vector Table (IVT) is a critical memory structure that stores the addresses of Interrupt Service Routines (ISRs), enabling the processor to quickly locate the appropriate ISR when an interrupt occurs. An ISR is a specialized function executed in response to an interrupt signal, allowing your system to handle asynchronous events efficiently. Understanding the relationship between the IVT and ISRs is essential for effective interrupt handling and ensuring timely response to hardware or software interrupts.

What is an Interrupt Vector Table (IVT)?

The Interrupt Vector Table (IVT) is a data structure in memory that holds the addresses of Interrupt Service Routines (ISRs) corresponding to various interrupt sources. When an interrupt occurs, the processor uses the IVT to quickly locate the appropriate ISR to execute, ensuring efficient handling of hardware and software interrupts. The IVT is critical in embedded systems and operating systems for managing interrupts and maintaining system stability.

Understanding Interrupt Service Routines (ISR)

The Interrupt Vector Table (IVT) holds memory addresses pointing to specific Interrupt Service Routines (ISRs) that the processor executes when an interrupt occurs. An ISR is a specialized function designed to quickly handle interrupts by addressing the hardware or software event and restoring normal program flow. Understanding how your system leverages the IVT to invoke the correct ISR is crucial for optimizing interrupt handling and improving real-time performance.

Key Differences Between IVT and ISR

The Interrupt Vector Table (IVT) is a data structure that stores the addresses of Interrupt Service Routines (ISRs) corresponding to various interrupt sources, enabling the CPU to quickly locate the correct ISR when an interrupt occurs. An ISR is a specific block of code executed in response to an interrupt, responsible for handling the event and restoring normal program flow. The key difference lies in their purpose: the IVT acts as a lookup table mapping interrupts to their handler addresses, while the ISR contains the actual handling logic executed by the processor.

The Role of IVT in Interrupt Management

The Interrupt Vector Table (IVT) serves as a critical map in interrupt management, storing pointers to the base addresses of Interrupt Service Routines (ISRs) corresponding to each interrupt request. It allows the processor to quickly locate and execute the correct ISR by using the interrupt vector as an index. Efficient IVT organization enhances system responsiveness by minimizing the delay between interrupt occurrence and ISR execution.

How ISRs Handle Hardware and Software Interrupts

Interrupt Service Routines (ISRs) manage hardware and software interrupts by executing specific code triggered through entries in the Interrupt Vector Table, which maps each interrupt source to its corresponding ISR address. When a hardware signal or software interrupt occurs, the processor uses the interrupt vector to locate and jump to the appropriate ISR, ensuring timely and accurate response. ISRs efficiently handle tasks like device communication or system calls by quickly addressing the interrupt cause and restoring normal program flow.

IVT Structure and Organization in Modern Systems

The Interrupt Vector Table (IVT) in modern systems is a structured memory area containing addresses of Interrupt Service Routines (ISRs) for efficient hardware interrupt handling. Each entry in the IVT corresponds to a specific interrupt type, enabling the processor to quickly locate and execute the appropriate ISR based on the interrupt vector number. Your system's IVT organization enhances interrupt response time by mapping hardware signals to ISR addresses, ensuring seamless and prioritized task management.

Best Practices for Writing Efficient ISRs

Efficient Interrupt Service Routines (ISRs) rely on a well-organized Interrupt Vector Table to quickly direct the processor to the correct handler, minimizing latency and ensuring timely response. Best practices for writing ISRs include keeping the code short and fast, avoiding heavy processing within the ISR, and deferring extensive tasks to the main program loop or separate threads. You should also ensure the ISR manages only the necessary context saving and restoring, and uses volatile qualifiers for shared variables to prevent optimization errors by the compiler.

Common Challenges in IVT and ISR Implementation

Common challenges in Interrupt Vector Table (IVT) and Interrupt Service Routine (ISR) implementation include ensuring correct and efficient mapping of interrupt vectors to their corresponding ISRs, which is critical for system stability and performance. Developers often face difficulties in managing nested interrupts and prioritizing multiple interrupt sources without causing latency or resource conflicts. Proper synchronization and context-saving mechanisms are essential to prevent data corruption and ensure that Your embedded system responds promptly and accurately to interrupt signals.

Conclusion: Choosing the Right Interrupt Handling Approach

Selecting the appropriate interrupt handling approach depends on system complexity and response time requirements. The Interrupt Vector Table offers fast, direct mapping of interrupt sources to service routines, ideal for performance-critical applications with multiple interrupt types. In contrast, a single ISR can simplify design but may introduce latency, making the vector table preferable for efficient, scalable interrupt management in embedded systems.

Interrupt Vector Table vs ISR Infographic

electrown.com

electrown.com