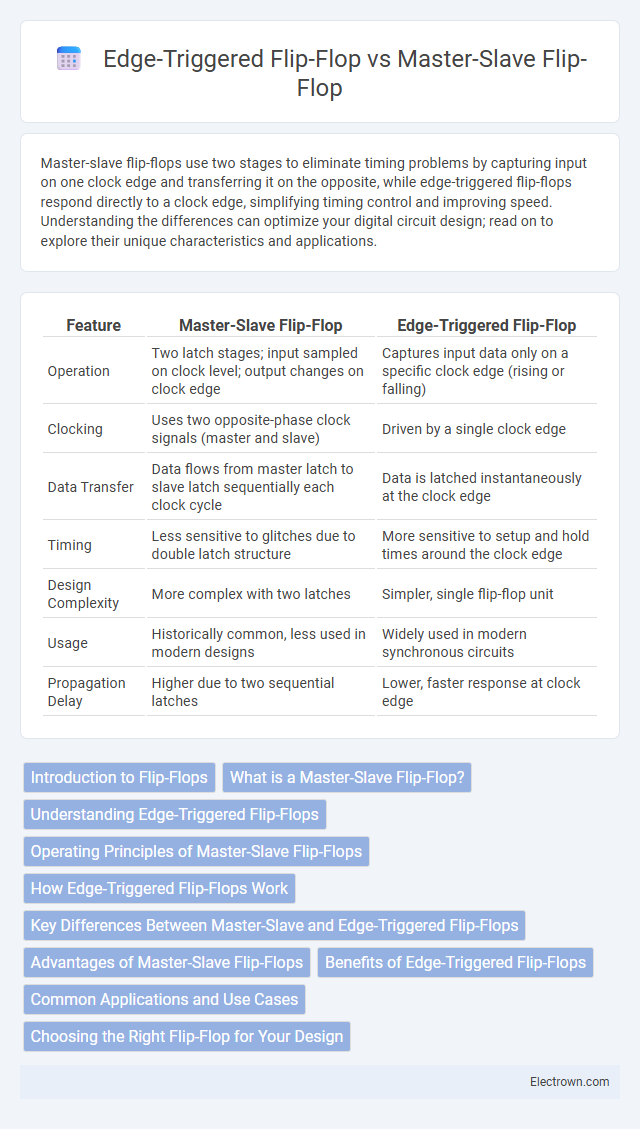

Master-slave flip-flops use two stages to eliminate timing problems by capturing input on one clock edge and transferring it on the opposite, while edge-triggered flip-flops respond directly to a clock edge, simplifying timing control and improving speed. Understanding the differences can optimize your digital circuit design; read on to explore their unique characteristics and applications.

Table of Comparison

| Feature | Master-Slave Flip-Flop | Edge-Triggered Flip-Flop |

|---|---|---|

| Operation | Two latch stages; input sampled on clock level; output changes on clock edge | Captures input data only on a specific clock edge (rising or falling) |

| Clocking | Uses two opposite-phase clock signals (master and slave) | Driven by a single clock edge |

| Data Transfer | Data flows from master latch to slave latch sequentially each clock cycle | Data is latched instantaneously at the clock edge |

| Timing | Less sensitive to glitches due to double latch structure | More sensitive to setup and hold times around the clock edge |

| Design Complexity | More complex with two latches | Simpler, single flip-flop unit |

| Usage | Historically common, less used in modern designs | Widely used in modern synchronous circuits |

| Propagation Delay | Higher due to two sequential latches | Lower, faster response at clock edge |

Introduction to Flip-Flops

Flip-flops are fundamental bistable devices used in digital circuits to store binary information, with their output depending on input signals and clock pulses. Master-slave flip-flops consist of two cascaded latches that prevent output changes during the active clock phase, enhancing data stability. Edge-triggered flip-flops capture input data precisely on clock signal transitions, ensuring synchronous and reliable timing in sequential logic designs.

What is a Master-Slave Flip-Flop?

A Master-Slave flip-flop is a type of bistable multivibrator composed of two flip-flops connected in series, where the first stage (master) captures the input on the clock pulse's active edge, and the second stage (slave) transfers this output on the clock's inactive edge, ensuring data stability and eliminating race conditions. This configuration prevents output changes during the clock pulse duration, making it ideal for synchronous sequential circuits requiring precise timing control. Master-Slave flip-flops are fundamental in digital systems for edge-sensitive data storage and timing synchronization.

Understanding Edge-Triggered Flip-Flops

Edge-triggered flip-flops capture and store data precisely at the triggering edge of the clock signal, either rising or falling, minimizing timing errors and improving synchronization in digital circuits. Unlike master-slave flip-flops that use two latches to handle data on both clock phases, edge-triggered flip-flops rely on a single latch activated only at the clock edge, ensuring more reliable and faster performance. This characteristic makes edge-triggered flip-flops essential in designing synchronous sequential logic systems where timing accuracy is critical.

Operating Principles of Master-Slave Flip-Flops

Master-slave flip-flops operate using two stages: the master latches the input on the clock's leading edge while the slave captures the master's output on the trailing edge, effectively preventing input changes during the clock pulse. This arrangement ensures synchronized and stable data transfer by controlling race conditions and glitches. The master stage samples the input when the clock is high, and the slave stage updates the output when the clock is low, enabling edge-triggered behavior.

How Edge-Triggered Flip-Flops Work

Edge-triggered flip-flops capture and store data only at the precise moment of a clock signal's rising or falling edge, ensuring that input changes are synchronized with the clock. Unlike master-slave configurations that use two stages to avoid timing issues, edge-triggered flip-flops rely on a single-stage design controlled by the clock edge, preventing input signal glitches from affecting the stored output. Understanding how edge-triggered flip-flops work can improve your ability to design stable and efficient digital circuits by ensuring reliable timing and data storage.

Key Differences Between Master-Slave and Edge-Triggered Flip-Flops

Master-Slave flip-flops utilize two stages where the master captures input on one clock phase and the slave updates output on the opposite phase, effectively preventing race conditions; edge-triggered flip-flops respond directly to a specific clock edge (rising or falling), simplifying timing and control. Master-Slave designs inherently introduce propagation delay due to the double latch mechanism, whereas edge-triggered flip-flops minimize delay by using a single stage triggered by the clock transition. Timing sensitivity differs as master-slave flip-flops are level-sensitive internally but edge-sensitive overall, while edge-triggered flip-flops exhibit pure edge sensitivity, enhancing performance in synchronous circuits.

Advantages of Master-Slave Flip-Flops

Master-Slave flip-flops offer improved noise immunity by eliminating glitches caused by direct clock signal transitions, ensuring stable data storage during the clock pulse. They provide better synchronization in sequential circuits by dividing the operation into two distinct phases, reducing timing issues inherent in edge-triggered designs. Your digital designs benefit from reliable state changes and reduced race conditions when using master-slave flip-flops in complex timing applications.

Benefits of Edge-Triggered Flip-Flops

Edge-triggered flip-flops offer precise timing control by capturing input data only at the clock edge, significantly reducing data corruption and race conditions common in master-slave configurations. This improves circuit reliability and performance, especially in high-speed digital systems where timing accuracy is critical. Their simplified timing requirements also enable easier design and testing in synchronous sequential circuits.

Common Applications and Use Cases

Master-Slave flip-flops are widely used in synchronous circuits such as shift registers and counters to avoid timing issues due to their edge-triggered behavior. Edge-triggered flip-flops are essential in digital systems requiring precise timing and data storage, such as microprocessor registers and memory elements. Both types are fundamental in designing reliable sequential logic circuits, with master-slave flip-flops preferred for eliminating race conditions and edge-triggered flip-flops favored for simplicity and speed.

Choosing the Right Flip-Flop for Your Design

Selecting the appropriate flip-flop between master-slave and edge-triggered types depends on timing requirements and circuit complexity. Master-slave flip-flops provide robust synchronization by using two sequential stages to prevent glitches, ideal for designs needing precise control over timing hazards. Edge-triggered flip-flops offer efficient operation with simpler timing through triggering at clock edges, making them preferable for high-speed, resource-constrained applications.

Master-Slave vs Edge-Triggered Flip-Flop Infographic

electrown.com

electrown.com