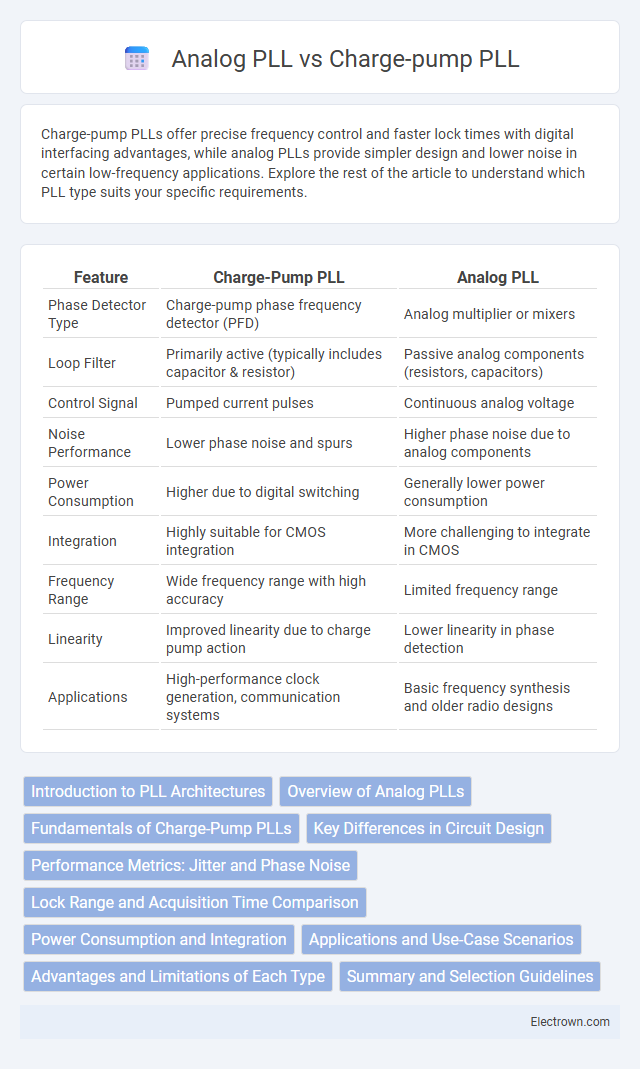

Charge-pump PLLs offer precise frequency control and faster lock times with digital interfacing advantages, while analog PLLs provide simpler design and lower noise in certain low-frequency applications. Explore the rest of the article to understand which PLL type suits your specific requirements.

Table of Comparison

| Feature | Charge-Pump PLL | Analog PLL |

|---|---|---|

| Phase Detector Type | Charge-pump phase frequency detector (PFD) | Analog multiplier or mixers |

| Loop Filter | Primarily active (typically includes capacitor & resistor) | Passive analog components (resistors, capacitors) |

| Control Signal | Pumped current pulses | Continuous analog voltage |

| Noise Performance | Lower phase noise and spurs | Higher phase noise due to analog components |

| Power Consumption | Higher due to digital switching | Generally lower power consumption |

| Integration | Highly suitable for CMOS integration | More challenging to integrate in CMOS |

| Frequency Range | Wide frequency range with high accuracy | Limited frequency range |

| Linearity | Improved linearity due to charge pump action | Lower linearity in phase detection |

| Applications | High-performance clock generation, communication systems | Basic frequency synthesis and older radio designs |

Introduction to PLL Architectures

Charge-pump PLLs utilize digital phase-frequency detectors and charge pumps to control the voltage-controlled oscillator, offering improved phase noise and frequency stability compared to traditional analog PLLs. Analog PLLs rely on continuous-time phase detectors and loop filters, resulting in simpler circuits but higher susceptibility to noise and less precision in frequency synthesis. Modern communication systems favor charge-pump PLL architectures for their enhanced linearity, lower jitter, and better integration with digital CMOS processes.

Overview of Analog PLLs

Analog Phase-Locked Loops (PLLs) use continuous-time components such as voltage-controlled oscillators (VCOs), phase detectors, and loop filters to synchronize output signals with reference inputs. Their design offers low phase noise and high-frequency stability, making them suitable for applications requiring precise frequency control. However, analog PLLs tend to have larger chip area and power consumption compared to charge-pump PLLs, and are more sensitive to component variations and noise.

Fundamentals of Charge-Pump PLLs

Charge-pump PLLs (Phase-Locked Loops) utilize discrete current sources to convert phase error signals into control voltages, enabling precise frequency synthesis and improved lock performance compared to traditional analog PLLs. The charge-pump mechanism generates pulses proportional to phase differences, which, when integrated by a loop filter, control the voltage-controlled oscillator (VCO) with enhanced linearity and stability. Your choice of a charge-pump PLL offers benefits in reduced phase noise and better immunity to reference spurs, critical for high-performance communication systems.

Key Differences in Circuit Design

Charge-pump PLLs feature discrete current sources controlled by phase-frequency detectors, enabling precise charge transfer to the loop filter, resulting in better frequency stability and lower phase noise compared to analog PLLs that rely on continuous voltage outputs. Analog PLLs use a continuous-time phase detector with a simple low-pass filter, which can lead to higher jitter due to voltage variations and less control over loop dynamics. The charge-pump architecture allows for finer loop bandwidth adjustments and improved integration in CMOS processes, making it preferable for high-performance frequency synthesis applications.

Performance Metrics: Jitter and Phase Noise

Charge-pump PLLs exhibit lower jitter and improved phase noise performance compared to analog PLLs due to their digital control and reduced sensitivity to component variations. Analog PLLs often suffer higher phase noise caused by continuous-time voltage-controlled oscillators and analog loop filters. The discrete-time nature of charge-pump PLLs enables better noise shaping and tighter timing resolution, making them superior for high-precision clock generation.

Lock Range and Acquisition Time Comparison

Charge-pump PLLs generally offer a wider lock range and faster acquisition time compared to analog PLLs due to their digital control of the voltage-controlled oscillator (VCO) frequency. The discrete nature of charge-pump PLLs allows more precise phase error detection and correction, enhancing lock-in speed and stability across varying frequencies. Analog PLLs tend to have narrower lock ranges and slower acquisition times because of continuous, less accurate phase detection and slower transient response.

Power Consumption and Integration

Charge-pump PLLs typically consume less power than analog PLLs due to their digital control and efficient current handling, making them ideal for battery-operated and low-power devices. Their compatibility with CMOS technology enables seamless integration into modern ICs, offering compact design and scalability. Your selection between the two should consider the power budget and integration requirements of your application for optimal performance.

Applications and Use-Case Scenarios

Charge-pump PLLs excel in high-frequency communication systems and clock generation for digital circuits, offering precise phase control and low jitter essential for modern microprocessors and wireless devices. Analog PLLs are preferred in audio processing, FM demodulation, and low-frequency applications where simplicity and continuous control voltage tuning are advantageous. Your choice depends on requirements for integration, noise performance, and operating frequency, with charge-pump PLLs favored in integrated CMOS designs and analog PLLs suitable for discrete or low-speed scenarios.

Advantages and Limitations of Each Type

Charge-pump PLLs offer precise frequency control and low phase noise, making them ideal for applications requiring high stability and integration with digital systems, but they can suffer from increased complexity and susceptibility to charge injection errors. Analog PLLs provide simpler design and faster locking speeds with lower power consumption, beneficial for cost-sensitive or low-frequency applications, yet they often exhibit higher phase noise and reduced integration flexibility. The choice between charge-pump and analog PLLs hinges on trade-offs between noise performance, integration level, complexity, and application-specific requirements.

Summary and Selection Guidelines

Charge-pump PLLs offer higher integration, better phase noise performance, and lower power consumption compared to analog PLLs, making them ideal for modern digital communication systems. Analog PLLs feature simpler designs and faster settling times but suffer from increased jitter and reduced flexibility in frequency synthesis. Your choice should depend on applications demanding precision and integration where charge-pump PLLs excel, whereas analog PLLs suit low-frequency or less complex requirements.

Charge-pump PLL vs analog PLL Infographic

electrown.com

electrown.com