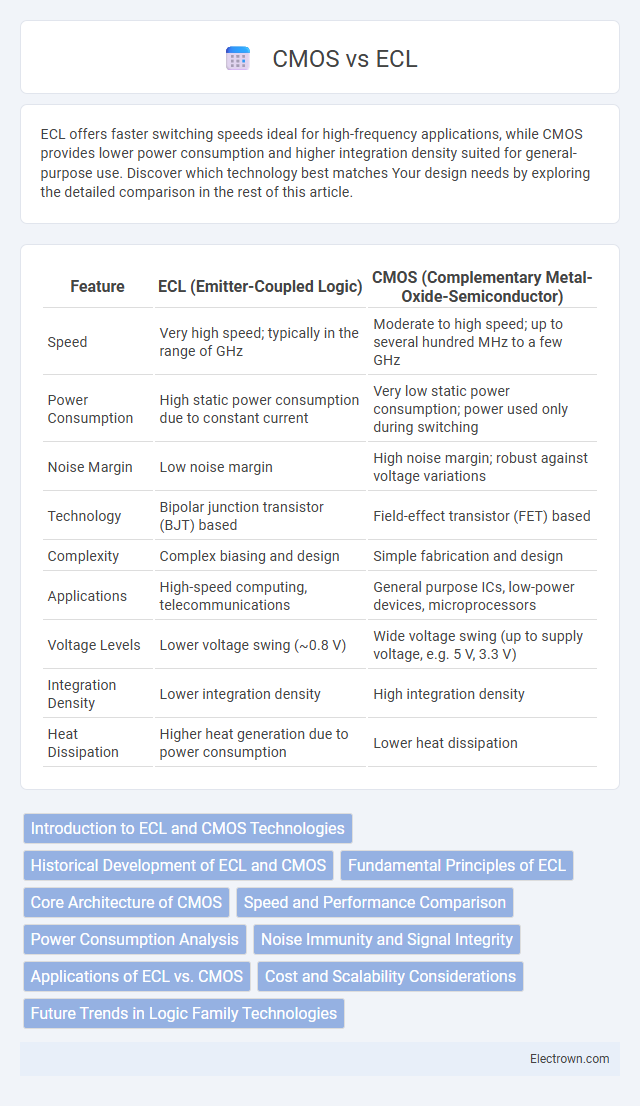

ECL offers faster switching speeds ideal for high-frequency applications, while CMOS provides lower power consumption and higher integration density suited for general-purpose use. Discover which technology best matches Your design needs by exploring the detailed comparison in the rest of this article.

Table of Comparison

| Feature | ECL (Emitter-Coupled Logic) | CMOS (Complementary Metal-Oxide-Semiconductor) |

|---|---|---|

| Speed | Very high speed; typically in the range of GHz | Moderate to high speed; up to several hundred MHz to a few GHz |

| Power Consumption | High static power consumption due to constant current | Very low static power consumption; power used only during switching |

| Noise Margin | Low noise margin | High noise margin; robust against voltage variations |

| Technology | Bipolar junction transistor (BJT) based | Field-effect transistor (FET) based |

| Complexity | Complex biasing and design | Simple fabrication and design |

| Applications | High-speed computing, telecommunications | General purpose ICs, low-power devices, microprocessors |

| Voltage Levels | Lower voltage swing (~0.8 V) | Wide voltage swing (up to supply voltage, e.g. 5 V, 3.3 V) |

| Integration Density | Lower integration density | High integration density |

| Heat Dissipation | Higher heat generation due to power consumption | Lower heat dissipation |

Introduction to ECL and CMOS Technologies

ECL (Emitter-Coupled Logic) and CMOS (Complementary Metal-Oxide-Semiconductor) represent two fundamental digital circuit technologies with distinct operational principles. ECL uses differential amplifier stages to achieve high-speed switching with minimal delay, making it ideal for applications requiring rapid signal processing. CMOS technology relies on complementary transistor pairs to minimize power consumption and heat generation, offering advantages in energy efficiency while maintaining scalability for complex integrated circuits.

Historical Development of ECL and CMOS

ECL (Emitter-Coupled Logic) was developed in the late 1950s as a high-speed digital logic family, utilizing bipolar transistors to achieve faster switching speeds than earlier logic families. CMOS (Complementary Metal-Oxide-Semiconductor) technology emerged in the late 1960s, gaining prominence due to its low power consumption and high integration density afforded by complementary p-type and n-type MOSFETs. The evolution of ECL focused on speed improvements in early computing systems, while CMOS advancements primarily enabled the miniaturization and energy efficiency of modern integrated circuits.

Fundamental Principles of ECL

Emitter-Coupled Logic (ECL) operates by avoiding transistor saturation and using differential amplifier configurations to achieve high-speed switching, making it faster than CMOS. ECL's constant current source and rapid switching transistors reduce propagation delay, which is critical in high-frequency applications. Understanding these fundamental principles can help optimize Your circuit designs for speed-sensitive environments.

Core Architecture of CMOS

The core architecture of CMOS (Complementary Metal-Oxide-Semiconductor) integrates both p-type and n-type MOSFETs to enable low static power consumption by ensuring that only one transistor type is conducting at a time. This complementary structure allows CMOS circuits to achieve high noise immunity and efficient switching characteristics, making it ideal for digital logic applications. Your choice of CMOS over ECL emphasizes energy efficiency and scalability in integrated circuit design.

Speed and Performance Comparison

ECL (Emitter-Coupled Logic) offers significantly higher speed than CMOS (Complementary Metal-Oxide-Semiconductor) due to its constant current operation and minimal voltage swing, resulting in propagation delays typically in the picosecond range. CMOS, while slower with nanosecond-scale delays, excels in power efficiency and integration density, making it ideal for large-scale digital circuits. Your choice between ECL and CMOS depends on prioritizing ultra-high-speed performance versus lower power consumption and device complexity.

Power Consumption Analysis

ECL (Emitter-Coupled Logic) circuits typically consume more power compared to CMOS (Complementary Metal-Oxide-Semiconductor) due to their constant current operation regardless of switching activity, leading to continuous power dissipation. CMOS technology significantly reduces power consumption by drawing current primarily during switching events, making it highly efficient for battery-powered and low-power applications. Your choice between ECL and CMOS should consider the trade-off between ECL's high speed and CMOS's superior energy efficiency.

Noise Immunity and Signal Integrity

ECL (Emitter-Coupled Logic) offers superior noise immunity compared to CMOS due to its differential signaling and constant current operation, which minimizes voltage fluctuations and susceptibility to electromagnetic interference. CMOS circuits, while more power-efficient, are more vulnerable to noise because of their high input impedance and single-ended voltage thresholds, making signal integrity a critical consideration in high-speed applications. When designing your system, prioritizing ECL can ensure enhanced signal integrity and reduced error rates in noisy environments.

Applications of ECL vs. CMOS

ECL (Emitter-Coupled Logic) excels in high-speed applications such as telecommunications, radar systems, and high-frequency signal processing due to its fast switching times and low propagation delay. CMOS (Complementary Metal-Oxide-Semiconductor) is widely used in power-sensitive and large-scale integration applications like microprocessors, sensors, and battery-operated devices because of its low static power consumption and high noise immunity. Choosing between ECL and CMOS depends on your specific requirements for speed versus power efficiency in your electronic design.

Cost and Scalability Considerations

ECL (Emitter Coupled Logic) circuits generally incur higher manufacturing costs due to their complex bipolar transistor design and increased power consumption compared to CMOS (Complementary Metal-Oxide-Semiconductor) technology. CMOS technology offers superior scalability, enabling the production of densely packed, low-power integrated circuits at a lower cost per transistor, which makes it the preferred choice for large-scale digital applications. While ECL provides faster switching speeds, CMOS dominates in cost efficiency and scalability for modern semiconductor manufacturing processes.

Future Trends in Logic Family Technologies

Future trends in logic family technologies highlight a gradual shift from traditional ECL (Emitter-Coupled Logic) to advanced CMOS (Complementary Metal-Oxide-Semiconductor) designs driven by power efficiency and scalability. CMOS technology continues to dominate due to its lower power consumption and higher integration density, enabling future logic devices with enhanced performance and miniaturization. Your design choices will increasingly favor CMOS innovations incorporating FinFET and gate-all-around (GAA) architectures to meet the demands of next-generation high-speed and low-power applications.

ECL vs CMOS Infographic

electrown.com

electrown.com