Asynchronous reset immediately forces the flip-flop to a known state regardless of the clock, providing fast response but potentially causing timing issues, while synchronous reset aligns reset signals with the clock, ensuring predictable timing but possibly introducing latency. Understanding these differences can help you choose the best reset strategy for your digital design--read on to explore the detailed trade-offs and implementation tips.

Table of Comparison

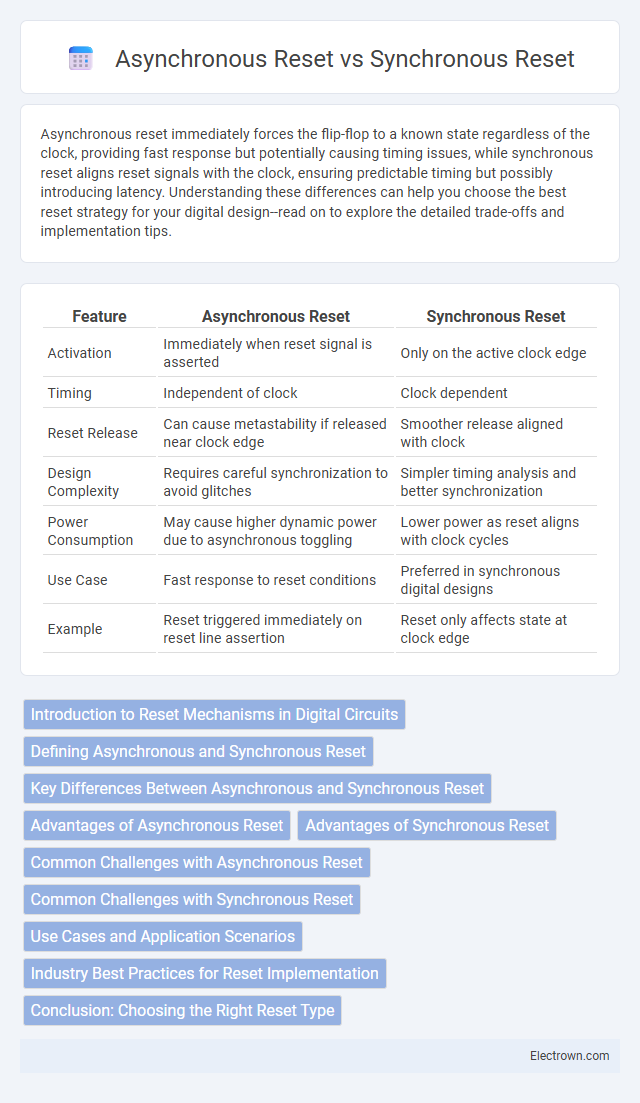

| Feature | Asynchronous Reset | Synchronous Reset |

|---|---|---|

| Activation | Immediately when reset signal is asserted | Only on the active clock edge |

| Timing | Independent of clock | Clock dependent |

| Reset Release | Can cause metastability if released near clock edge | Smoother release aligned with clock |

| Design Complexity | Requires careful synchronization to avoid glitches | Simpler timing analysis and better synchronization |

| Power Consumption | May cause higher dynamic power due to asynchronous toggling | Lower power as reset aligns with clock cycles |

| Use Case | Fast response to reset conditions | Preferred in synchronous digital designs |

| Example | Reset triggered immediately on reset line assertion | Reset only affects state at clock edge |

Introduction to Reset Mechanisms in Digital Circuits

Reset mechanisms in digital circuits initialize registers and sequential elements to a known state, ensuring predictable startup behavior. Asynchronous reset triggers immediately upon activation, independent of the clock signal, providing rapid system initialization, while synchronous reset asserts only at clock edges, aligning resets with timing sequences to avoid metastability. Understanding these mechanisms is critical for designing reliable state machines and embedded systems.

Defining Asynchronous and Synchronous Reset

Asynchronous reset immediately forces a digital circuit into a predefined state regardless of the clock signal, ensuring rapid system initialization or recovery during power-up or fault conditions. Synchronous reset relies on the clock edge to activate the reset, allowing the circuit to reset states in alignment with the clock timing, which helps maintain predictable timing behavior in sequential logic. Understanding the distinction between asynchronous and synchronous reset is crucial for designing reliable and robust digital systems tailored to specific timing and control requirements.

Key Differences Between Asynchronous and Synchronous Reset

Asynchronous reset immediately forces a flip-flop or register to a predefined state regardless of the clock signal, enabling rapid recovery from errors or initialization conditions. Synchronous reset occurs only in sync with the clock edge, ensuring that all registers reset simultaneously within the clock domain, which helps avoid timing issues. Understanding these key differences helps optimize your digital design's reliability and timing performance.

Advantages of Asynchronous Reset

Asynchronous reset offers the advantage of immediate response to reset signals, ensuring rapid initialization of digital circuits regardless of the clock state. This characteristic enhances reliability in critical applications where your system must quickly recover from faults or power-up conditions. The independence from clock edges also simplifies timing analysis and reduces latency in resetting flip-flops and registers.

Advantages of Synchronous Reset

Synchronous reset offers precise timing control since the reset signal is synchronized with the clock, reducing the risk of metastability and glitches in digital circuits. It ensures predictable state transitions and simplifies timing analysis, optimizing the design for high-speed applications. This reset type integrates smoothly with synchronous design methodologies, improving overall circuit reliability and ease of implementation.

Common Challenges with Asynchronous Reset

Asynchronous reset circuits often face issues like metastability and timing violations due to their immediate response to reset signals irrespective of the clock edge. This can cause unpredictable behavior in flip-flops and introduce glitches in sequential logic, leading to unreliable system performance. Designers must carefully manage reset de-assertion timing and employ synchronization techniques to mitigate these common challenges.

Common Challenges with Synchronous Reset

Synchronous reset can cause timing challenges as it relies on the clock edge, potentially leading to reset deassertion being delayed or missed if clock glitches occur. Setup and hold violations around the clock can introduce metastability, making it difficult to guarantee reliable system initialization. Your design may also face increased complexity when ensuring that multiple flip-flops release reset simultaneously, risking inconsistent states during startup.

Use Cases and Application Scenarios

Asynchronous reset is ideal for critical system-wide resets where immediate response to a reset signal is necessary, such as in power-up initialization or emergency shutdowns. Synchronous reset fits well in clocked digital systems where reset signals must align with the clock to prevent metastability and ensure predictable timing, commonly used in FPGA designs and sequential circuits. Understanding your system's timing requirements and reset responsiveness helps determine the best choice between asynchronous and synchronous resets for reliable operation.

Industry Best Practices for Reset Implementation

Industry best practices for reset implementation emphasize using synchronous resets in FPGA and ASIC designs to ensure predictable timing and easier timing closure. Asynchronous resets are often avoided due to potential metastability and reset release timing issues, which can cause unpredictable behavior. Designers frequently implement synchronized reset de-assertion circuits to combine the reliability of asynchronous reset initiation with the timing benefits of synchronous reset release.

Conclusion: Choosing the Right Reset Type

Choosing between asynchronous and synchronous reset depends on the specific design requirements such as timing constraints and complexity. Asynchronous resets offer immediate state initialization, beneficial for fast recovery but may introduce metastability risks. Synchronous resets align with the clock, providing controlled state changes and easier timing analysis, making them preferable for clean, predictable designs.

Asynchronous Reset vs Synchronous Reset Infographic

electrown.com

electrown.com