Static logic uses a fixed voltage level for logic states, resulting in simplicity and low power consumption, while dynamic logic relies on temporary voltage storage and clock cycles for faster processing speeds but increased complexity and power use. Discover how understanding static vs dynamic logic can optimize Your circuit design by exploring the benefits and trade-offs in the full article.

Table of Comparison

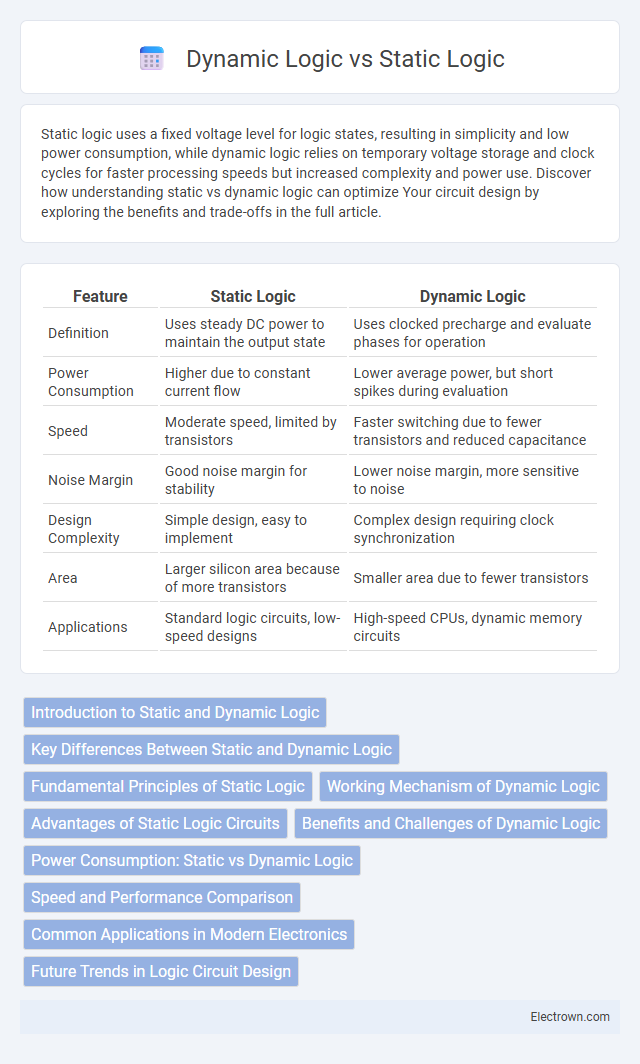

| Feature | Static Logic | Dynamic Logic |

|---|---|---|

| Definition | Uses steady DC power to maintain the output state | Uses clocked precharge and evaluate phases for operation |

| Power Consumption | Higher due to constant current flow | Lower average power, but short spikes during evaluation |

| Speed | Moderate speed, limited by transistors | Faster switching due to fewer transistors and reduced capacitance |

| Noise Margin | Good noise margin for stability | Lower noise margin, more sensitive to noise |

| Design Complexity | Simple design, easy to implement | Complex design requiring clock synchronization |

| Area | Larger silicon area because of more transistors | Smaller area due to fewer transistors |

| Applications | Standard logic circuits, low-speed designs | High-speed CPUs, dynamic memory circuits |

Introduction to Static and Dynamic Logic

Static logic uses stable voltage levels to represent binary states, offering simplicity, robustness, and low noise susceptibility, making it ideal for straightforward digital circuits. Dynamic logic relies on clocked precharge and evaluation phases to achieve faster switching speeds and reduced transistor count, enhancing performance in high-speed applications. Understanding the trade-offs between static and dynamic logic helps optimize your circuit design for power, speed, and complexity requirements.

Key Differences Between Static and Dynamic Logic

Static logic uses a constant precharged node evaluated by transistors, resulting in simpler design and less susceptibility to noise, while dynamic logic relies on clocked precharge and evaluation phases, allowing faster operation and reduced transistor count. Static logic circuits are robust with no need for clocking signals, but often have higher power consumption and slower speeds compared to dynamic logic, which improves speed and area efficiency but requires careful timing control to avoid glitches. Your choice between static and dynamic logic impacts circuit performance, power efficiency, and design complexity based on these fundamental differences.

Fundamental Principles of Static Logic

Static logic relies on CMOS technology where both PMOS and NMOS transistors create stable voltage levels through complementary action, ensuring reliable logic states without the need for continuous clocking. It uses pull-up and pull-down networks to maintain output levels, minimizing power consumption during steady-state operation. Your designs benefit from static logic's robustness in noise margins and simpler timing requirements compared to dynamic logic circuits.

Working Mechanism of Dynamic Logic

Dynamic logic operates using a precharge and evaluation phase, where the output node is initially precharged to a high voltage level before evaluating the inputs. During the evaluation phase, active transistors discharge the output node based on the input signals, thereby determining the logic state. This technique allows for faster switching speeds and reduced transistor count compared to static logic, but it requires careful clock synchronization to prevent erroneous evaluations.

Advantages of Static Logic Circuits

Static logic circuits offer several advantages including low power consumption since they do not require constant clocking to maintain their output state. They provide robust noise margins and are immune to dynamic hazards, ensuring stable and reliable operation in various environments. Your designs benefit from simpler implementation and reduced complexity compared to dynamic logic, making static logic ideal for low-power and high-reliability applications.

Benefits and Challenges of Dynamic Logic

Dynamic logic offers faster operation speeds and reduced transistor count compared to static logic, enabling higher performance in complex digital circuits. Its benefits include increased switching speed and lower power consumption during switching events, making it ideal for high-frequency applications. Challenges involve susceptibility to noise, charge sharing, and the need for careful clocking schemes to prevent logic errors and ensure reliable operation.

Power Consumption: Static vs Dynamic Logic

Static logic circuits consume power primarily due to leakage currents during idle states, offering lower dynamic power consumption compared to dynamic logic. Dynamic logic circuits exhibit higher power consumption because of constant charging and discharging of capacitances in clocked precharge and evaluation phases, leading to increased dynamic power use. Overall, static logic is more power-efficient for low-frequency or low-activity designs, whereas dynamic logic suits high-speed applications despite higher power demands.

Speed and Performance Comparison

Dynamic logic circuits generally achieve higher speed and better performance than static logic due to reduced transistor count and fewer parasitic capacitances, enabling faster switching. Static logic offers greater noise immunity and lower power consumption but typically suffers from slower propagation delays. Choosing the right logic style for your design depends on balancing speed requirements with power efficiency and noise tolerance.

Common Applications in Modern Electronics

Static logic circuits are widely used in low-power applications such as microprocessors, memory devices, and digital control systems due to their reliable and noise-immune operation. Dynamic logic is favored in high-speed digital circuits like advanced microprocessors, digital signal processors (DSPs), and high-frequency communication systems because of its superior speed and area efficiency. Understanding the trade-offs between static and dynamic logic helps you optimize performance and power consumption in modern electronic designs.

Future Trends in Logic Circuit Design

Future trends in logic circuit design emphasize the integration of adaptive hybrid logic styles combining static and dynamic logic to enhance power efficiency and speed. Emerging technologies focus on minimizing leakage currents and variability through advanced transistor scaling and novel materials such as FinFETs and gate-all-around FETs. Machine learning-driven design automation tools are increasingly used to optimize logic circuits for next-generation applications in AI and IoT, pushing boundaries in low-power, high-performance computing.

Static Logic vs Dynamic Logic Infographic

electrown.com

electrown.com