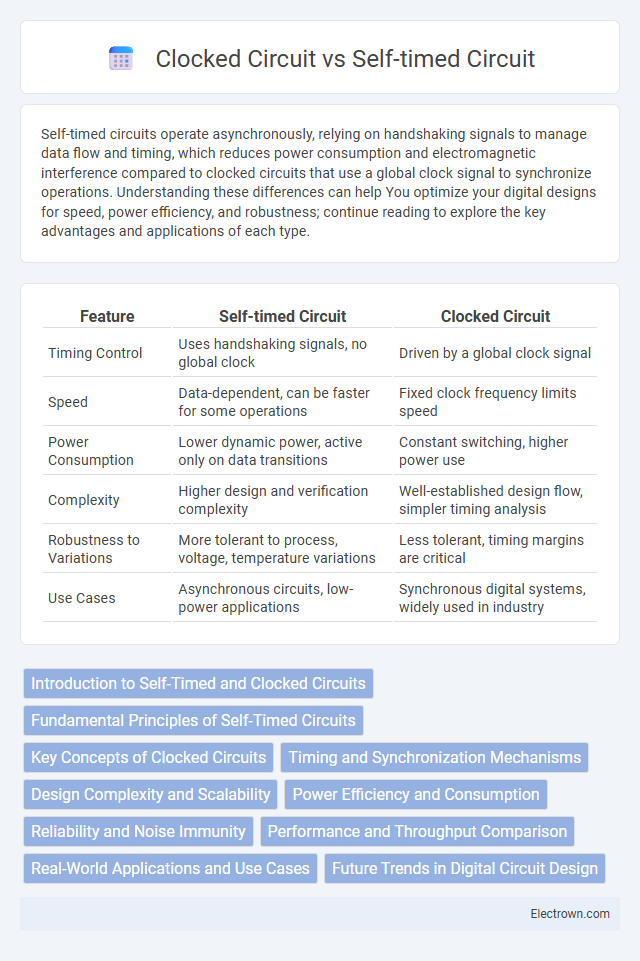

Self-timed circuits operate asynchronously, relying on handshaking signals to manage data flow and timing, which reduces power consumption and electromagnetic interference compared to clocked circuits that use a global clock signal to synchronize operations. Understanding these differences can help You optimize your digital designs for speed, power efficiency, and robustness; continue reading to explore the key advantages and applications of each type.

Table of Comparison

| Feature | Self-timed Circuit | Clocked Circuit |

|---|---|---|

| Timing Control | Uses handshaking signals, no global clock | Driven by a global clock signal |

| Speed | Data-dependent, can be faster for some operations | Fixed clock frequency limits speed |

| Power Consumption | Lower dynamic power, active only on data transitions | Constant switching, higher power use |

| Complexity | Higher design and verification complexity | Well-established design flow, simpler timing analysis |

| Robustness to Variations | More tolerant to process, voltage, temperature variations | Less tolerant, timing margins are critical |

| Use Cases | Asynchronous circuits, low-power applications | Synchronous digital systems, widely used in industry |

Introduction to Self-Timed and Clocked Circuits

Self-timed circuits operate based on data-driven handshaking protocols, eliminating the need for a global clock and allowing asynchronous operation that adapts to variable processing speeds. Clocked circuits rely on a centralized clock signal that synchronizes all circuit components, ensuring a fixed timing schedule but potentially causing inefficiencies due to clock skew and idle waiting times. The fundamental difference lies in timing control: self-timed circuits use local completion detection for each operation, while clocked circuits use periodic clock edges to coordinate state transitions.

Fundamental Principles of Self-Timed Circuits

Self-timed circuits operate based on the completion of internal events rather than relying on a global clock signal, enabling asynchronous data flow and reducing power consumption. These circuits use handshaking protocols and delay-insensitive data encoding to manage timing and signal integrity, making them robust against variations in processing speed and environmental conditions. Understanding the fundamental principles of self-timed circuits allows you to design systems that enhance performance and resilience where timing uncertainty is critical.

Key Concepts of Clocked Circuits

Clocked circuits operate based on a global clock signal that synchronizes state changes, enabling predictable timing and easier design verification. They rely on flip-flops and latches triggered by clock edges, which ensures uniform data sampling intervals and simplifies timing analysis. This structured timing framework makes clocked circuits suitable for high-speed, complex digital systems requiring precise coordination.

Timing and Synchronization Mechanisms

Self-timed circuits rely on local handshaking protocols to manage timing and synchronization, eliminating the need for a global clock signal and reducing clock skew issues. Clocked circuits use a centralized clock to synchronize all operations, ensuring uniform timing but potentially introducing timing bottlenecks and clock distribution challenges. Your design choice impacts system robustness, power consumption, and timing complexity based on these distinct synchronization mechanisms.

Design Complexity and Scalability

Self-timed circuits reduce design complexity by eliminating the global clock, allowing modules to operate independently and adapt to process variations, which enhances scalability in large systems. Clocked circuits demand precise timing and synchronization, increasing complexity as system size grows due to clock distribution and skew management challenges. Your choice between these architectures should consider the trade-off between simplicity and control over timing for scalable designs.

Power Efficiency and Consumption

Self-timed circuits significantly reduce power consumption by eliminating the global clock, enabling components to operate only when required, which minimizes switching activity and dynamic power usage. Clocked circuits rely on a continuous clock signal that triggers all components simultaneously, resulting in higher power consumption due to unnecessary transitions and increased dynamic power dissipation even when parts of the circuit are idle. This asynchronous operation in self-timed designs leads to improved power efficiency, making them suitable for low-power applications and environments with variable workloads.

Reliability and Noise Immunity

Self-timed circuits offer enhanced reliability and superior noise immunity by eliminating the global clock, allowing modules to operate asynchronously and adapt dynamically to processing delays and environmental variations. Clocked circuits rely heavily on a periodic clock signal, making them more susceptible to clock skew, jitter, and electromagnetic interference, which can compromise timing accuracy and increase error rates. Consequently, self-timed designs excel in low-power, high-robustness applications where minimizing timing errors and noise sensitivity is critical.

Performance and Throughput Comparison

Self-timed circuits often achieve higher performance by eliminating clock skew and allowing modules to operate asynchronously, resulting in reduced latency and improved throughput under variable workloads. Clocked circuits rely on a global clock, which can introduce synchronization delays and limit maximum frequency, thereby potentially reducing throughput in high-speed applications. The asynchronous nature of self-timed designs enables finer-grained control over data propagation, often leading to more efficient resource utilization and enhanced overall system performance.

Real-World Applications and Use Cases

Self-timed circuits excel in low-power and asynchronous environments such as sensor networks, biomedical devices, and adaptive computing, where timing variability and power efficiency are critical. Clocked circuits dominate in high-performance applications including microprocessors, digital signal processing, and synchronous communication systems due to their predictable timing and ease of design verification. Your choice depends on whether energy efficiency or timing predictability is the priority in the target application.

Future Trends in Digital Circuit Design

Self-timed circuits offer significant advantages in future digital circuit design by enabling asynchronous operation, which reduces power consumption and mitigates clock skew issues prevalent in clocked circuits. Advances in adaptive timing and formal verification techniques are driving the adoption of self-timed designs for more efficient, scalable, and reliable systems. Your choice between self-timed and clocked circuits will impact the optimization of speed, energy efficiency, and overall system robustness as digital technologies evolve.

Self-timed circuit vs clocked circuit Infographic

electrown.com

electrown.com