Setup time violation occurs when a data signal fails to stabilize before the clock edge, causing incorrect data to be latched, while hold time violation happens when data changes too soon after the clock edge, risking data corruption. Understanding these timing issues is crucial for ensuring reliable digital circuit performance, so continue reading to explore how to identify and resolve setup and hold time violations effectively.

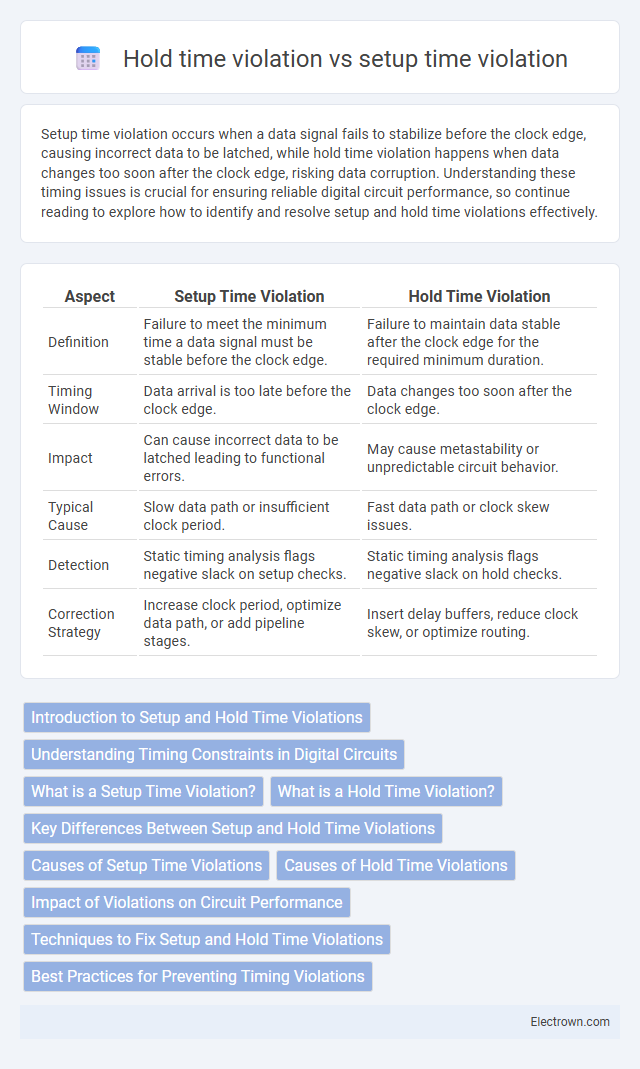

Table of Comparison

| Aspect | Setup Time Violation | Hold Time Violation |

|---|---|---|

| Definition | Failure to meet the minimum time a data signal must be stable before the clock edge. | Failure to maintain data stable after the clock edge for the required minimum duration. |

| Timing Window | Data arrival is too late before the clock edge. | Data changes too soon after the clock edge. |

| Impact | Can cause incorrect data to be latched leading to functional errors. | May cause metastability or unpredictable circuit behavior. |

| Typical Cause | Slow data path or insufficient clock period. | Fast data path or clock skew issues. |

| Detection | Static timing analysis flags negative slack on setup checks. | Static timing analysis flags negative slack on hold checks. |

| Correction Strategy | Increase clock period, optimize data path, or add pipeline stages. | Insert delay buffers, reduce clock skew, or optimize routing. |

Introduction to Setup and Hold Time Violations

Setup time violation occurs when data fails to arrive at the flip-flop's input before the clock edge, risking incorrect data capture. Hold time violation happens when data changes too soon after the clock edge, causing instability in storage elements. Understanding these timing constraints ensures your digital circuit operates reliably within designed performance margins.

Understanding Timing Constraints in Digital Circuits

Setup time violation occurs when data input to a flip-flop changes too close to the clock edge, preventing stable data capture, while hold time violation happens when data changes immediately after the clock edge, causing incorrect data retention. Proper timing constraints ensure data signals meet the minimum setup and hold time requirements to maintain reliable sequential circuit operation. Violations of these constraints lead to metastability and functional errors, making precise timing analysis essential in digital design.

What is a Setup Time Violation?

A Setup Time Violation occurs when a data signal fails to remain stable for a required minimum duration before the clock edge triggers a latch or flip-flop, leading to incorrect data capture. This violation disrupts synchronous circuit timing by causing metastability or data corruption, impacting system reliability. Setup time is critical in digital design to ensure the flip-flop correctly registers input data on the clock transition.

What is a Hold Time Violation?

A hold time violation occurs when data changes too soon after the clock edge, causing incorrect data capture in sequential circuits. This violation happens if the data input to a flip-flop or latch does not remain stable for the required hold time duration following the clock transition. Proper timing analysis ensures that the data signal meets the hold time constraint to maintain circuit reliability and prevent metastability.

Key Differences Between Setup and Hold Time Violations

Setup time violation occurs when data does not arrive early enough before the clock edge, causing incorrect data to be latched, while hold time violation happens when data changes too soon after the clock edge, disrupting stable data capture. Setup violations result in metastability and data corruption at flip-flops, whereas hold violations lead to unintended data overwrites immediately after a clock transition. Understanding these key timing constraints is crucial for Your digital circuit design to ensure reliable synchronous operation and prevent logic errors.

Causes of Setup Time Violations

Setup time violations occur when data signals arrive too late to be reliably captured by the clock edge, often caused by excessive data path delays or slow combinational logic. Variations in clock skew, jitter, or insufficient clock period also contribute to setup time violations. Optimizing timing paths and reducing data latency are critical steps to prevent these violations in synchronous circuits.

Causes of Hold Time Violations

Hold time violations occur when data changes too quickly after a clock edge, preventing the receiving flip-flop from correctly capturing the signal. The primary causes include insufficient data path delay, clock skew causing early clock arrival, and variability in signal propagation times due to process, voltage, and temperature changes. To fix hold time violations, you can insert delay buffers or adjust clock distribution to ensure data remains stable during the required hold window.

Impact of Violations on Circuit Performance

Setup time violations cause data to be captured incorrectly at flip-flops, leading to timing errors and potential system malfunction, significantly degrading circuit reliability and speed. Hold time violations result in data instability immediately after a clock edge, causing metastability and unpredictable circuit behavior that can disrupt synchronous operation. Ensuring your design meets both setup and hold time requirements is critical to maintaining optimal performance and avoiding timing-related failures.

Techniques to Fix Setup and Hold Time Violations

Setup time violations are addressed by increasing the clock period, adding pipeline stages, or optimizing logic paths to reduce data arrival delay before the clock edge. Hold time violations can be fixed by inserting delay elements, using faster clock buffers, or rebalancing data paths to ensure data remains stable after the clock edge. Both techniques require careful timing analysis and may involve adjusting clock skew or redesigning critical paths to meet timing constraints.

Best Practices for Preventing Timing Violations

To prevent setup time violations, ensure your clock period is sufficiently longer than the maximum data propagation delay plus setup time, and optimize clock skew using balanced clock distribution networks. For hold time violations, introduce deliberate delay elements or adjust data launching circuits to avoid data arriving too early relative to the clock edge. Your design should incorporate static timing analysis (STA) tools to identify and fix timing violations proactively during the synthesis and place-and-route stages.

Setup time violation vs hold time violation Infographic

electrown.com

electrown.com