Metastability occurs when a digital circuit fails to settle into a stable logical state within the expected time, often leading to unpredictable outputs, while hazards are unwanted transient glitches caused by differences in signal delay in combinational logic. Understanding how metastability and hazards affect circuit reliability is crucial for designing robust digital systems; explore the rest of this article to deepen Your knowledge on managing these challenges effectively.

Table of Comparison

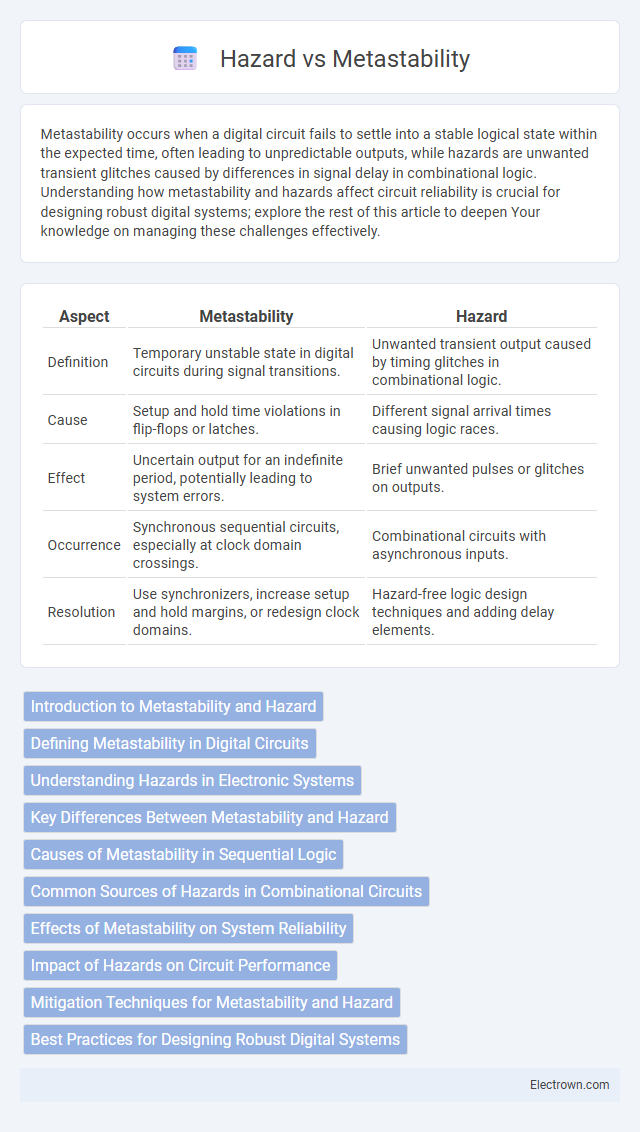

| Aspect | Metastability | Hazard |

|---|---|---|

| Definition | Temporary unstable state in digital circuits during signal transitions. | Unwanted transient output caused by timing glitches in combinational logic. |

| Cause | Setup and hold time violations in flip-flops or latches. | Different signal arrival times causing logic races. |

| Effect | Uncertain output for an indefinite period, potentially leading to system errors. | Brief unwanted pulses or glitches on outputs. |

| Occurrence | Synchronous sequential circuits, especially at clock domain crossings. | Combinational circuits with asynchronous inputs. |

| Resolution | Use synchronizers, increase setup and hold margins, or redesign clock domains. | Hazard-free logic design techniques and adding delay elements. |

Introduction to Metastability and Hazard

Metastability occurs in digital circuits when a flip-flop or latch fails to settle into a stable logical state within the required time, potentially causing unpredictable behavior. Hazards are unwanted transient glitches in combinational logic, arising from variable signal propagation delays and leading to temporary incorrect outputs. Understanding metastability and hazards is critical for designing robust synchronous systems that maintain data integrity and reliable timing.

Defining Metastability in Digital Circuits

Metastability in digital circuits occurs when a flip-flop or latch fails to resolve to a stable logic level within a clock period due to setup or hold time violations, leading to unpredictable outputs. This phenomenon arises from asynchronous inputs that violate timing constraints, causing the circuit to reside temporarily in an indeterminate state. Unlike hazards, which are brief unwanted switching transients, metastability poses a risk of prolonged uncertainty, undermining reliable data synchronization and system stability.

Understanding Hazards in Electronic Systems

Hazards in electronic systems are unintended transient changes in signal outputs that can cause glitches or errors during switching events. These hazards arise due to differences in path delays and timing mismatches in combinational logic, leading to momentary inconsistencies before the output stabilizes. Understanding hazard classification, including static and dynamic hazards, is crucial for designing robust circuits that minimize erroneous behavior in digital and asynchronous systems.

Key Differences Between Metastability and Hazard

Metastability occurs when a digital circuit enters an unstable state between logic levels due to timing violations, while a hazard is a momentary glitch caused by differing signal arrival times in combinational logic. Metastability can lead to unpredictable outputs in flip-flops or latches, impacting system reliability, whereas hazards produce transient, often harmless, glitches that do not usually affect the final output. Understanding these key differences helps you design more robust synchronous circuits by implementing proper synchronization techniques to minimize metastability and hazard risks.

Causes of Metastability in Sequential Logic

Metastability in sequential logic arises primarily from timing violations, such as setup and hold time failures, where input signals change too close to the clock edge. This condition causes flip-flops to enter an undefined intermediate state, delaying the output transition and potentially leading to erroneous behavior. Understanding and mitigating these timing issues in your design can reduce the risks associated with metastability, distinct from hazards that result from combinational logic glitches.

Common Sources of Hazards in Combinational Circuits

Common sources of hazards in combinational circuits include glitches caused by inconsistent signal propagation delays, race conditions arising from conflicting logic paths, and asynchronous input transitions that violate setup and hold times. These hazards lead to momentary incorrect outputs, affecting circuit reliability and performance. Understanding hazards is critical for designing robust digital systems and avoiding metastability in sequential elements receiving such glitch-prone signals.

Effects of Metastability on System Reliability

Metastability causes unpredictable delays in digital circuits, leading to timing violations and data corruption, which significantly reduce system reliability. It often occurs in asynchronous clock domain crossings, where flip-flops fail to resolve stable states within the required clock period. Prolonged metastable states increase error rates and system failures, necessitating robust synchronization techniques to mitigate these risks.

Impact of Hazards on Circuit Performance

Hazards in digital circuits cause unintended switching, leading to glitches that can degrade circuit performance and reliability. These transient errors may trigger metastability in flip-flops, causing uncertain output states and timing violations. Effective hazard mitigation is crucial for maintaining signal integrity and ensuring stable, predictable system operation.

Mitigation Techniques for Metastability and Hazard

Mitigation techniques for metastability focus on synchronizer design, such as using multiple flip-flop stages to reduce the probability of synchronization failure in asynchronous signal crossings. Hazard mitigation employs logic design strategies like hazard-free coding, insertion of delay elements, and using hazard-detecting circuits to ensure stable outputs despite input transitions. Both approaches enhance system reliability by minimizing timing uncertainties and logic glitches in digital circuits.

Best Practices for Designing Robust Digital Systems

To design robust digital systems, prioritize techniques such as synchronizer circuits to mitigate metastability, which occurs when signals fail to settle into a stable logic level during clock domain crossings. Implement hazard-free logic design by using proper timing constraints and hazard analysis tools to prevent glitches caused by asynchronous signal transitions. Employ multi-stage flip-flops and ensure adequate setup and hold times to reduce metastability risk, while simultaneously designing hazard-free combinational logic using consensus terms and hazard elimination methods.

Metastability vs Hazard Infographic

electrown.com

electrown.com