Race-around condition occurs in digital circuits when multiple signals compete to control the output simultaneously, causing unpredictable behavior, whereas a hold state refers to a period during which a signal or output is intentionally kept stable to ensure proper data storage or processing. Understanding the difference between these concepts is crucial for designing reliable synchronous circuits; explore the rest of the article to learn how to manage these issues effectively.

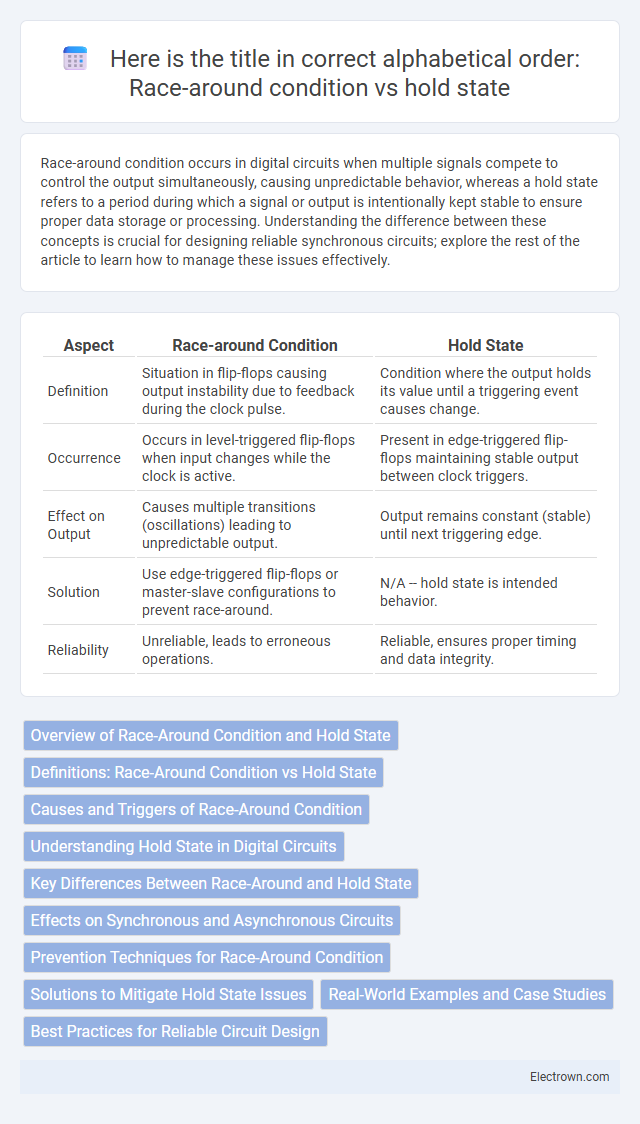

Table of Comparison

| Aspect | Race-around Condition | Hold State |

|---|---|---|

| Definition | Situation in flip-flops causing output instability due to feedback during the clock pulse. | Condition where the output holds its value until a triggering event causes change. |

| Occurrence | Occurs in level-triggered flip-flops when input changes while the clock is active. | Present in edge-triggered flip-flops maintaining stable output between clock triggers. |

| Effect on Output | Causes multiple transitions (oscillations) leading to unpredictable output. | Output remains constant (stable) until next triggering edge. |

| Solution | Use edge-triggered flip-flops or master-slave configurations to prevent race-around. | N/A -- hold state is intended behavior. |

| Reliability | Unreliable, leads to erroneous operations. | Reliable, ensures proper timing and data integrity. |

Overview of Race-Around Condition and Hold State

Race-around condition occurs in digital circuits when multiple signals change simultaneously, causing unpredictable output due to feedback loops. Hold state refers to a stable condition where the circuit maintains its current output until a new input triggers a change. Understanding these phenomena helps you design reliable sequential logic circuits that avoid timing hazards and data corruption.

Definitions: Race-Around Condition vs Hold State

A race-around condition occurs in sequential circuits when multiple inputs change simultaneously, causing conflicting outputs due to feedback loops, especially in JK flip-flops during high clock pulses. A hold state refers to the scenario where input signals must be maintained stable for a specified interval after a clock edge to ensure correct data capture and prevent timing violations. Distinguishing them is crucial in digital design to avoid unreliable circuit behavior and data corruption.

Causes and Triggers of Race-Around Condition

Race-around condition occurs in flip-flops when the propagation delay allows the output to change multiple times within a single clock pulse, triggered by high clock frequency and feedback loops in sequential circuits. Hold state refers to the stable phase in flip-flops where input changes do not affect the output, ensuring data stability. Your design must carefully manage clock timing and feedback to prevent race-around conditions that cause unpredictable data states.

Understanding Hold State in Digital Circuits

Hold state in digital circuits is a critical timing parameter ensuring that input signals remain stable for a specified period after the clock edge to prevent data corruption. Unlike race-around conditions that cause unpredictable output glitches due to feedback delays in flip-flops, hold state violations occur when data changes too soon, potentially leading to metastability. Understanding and properly designing for hold state requirements protects Your circuit's reliability and maintains accurate data transfer in synchronous systems.

Key Differences Between Race-Around and Hold State

Race-around conditions occur in JK flip-flops when both inputs are high, causing continuous toggling due to the feedback loop, while hold states refer to stable output conditions maintained by keeping inputs unchanged. The race-around phenomenon leads to unpredictable output changes within the clock pulse width, whereas hold state ensures output stability by preserving previous states during no input transitions. Understanding these differences is crucial for designing reliable sequential circuits with proper timing constraints.

Effects on Synchronous and Asynchronous Circuits

Race-around conditions cause unpredictable behavior in synchronous circuits by creating timing hazards that lead to erroneous outputs during clock transitions. In asynchronous circuits, hold state problems can result in metastability, where the circuit remains in an undefined state, delaying signal stabilization and affecting overall system reliability. Your design must carefully manage timing constraints to prevent race-around effects in synchronous circuits and hold violations in asynchronous circuits, ensuring accurate and stable operation.

Prevention Techniques for Race-Around Condition

Race-around conditions can be prevented by using edge-triggered flip-flops instead of level-triggered latches, ensuring state changes occur only at clock edges. Implementing master-slave flip-flop configurations effectively eliminates race-around issues by isolating input and output stages. Adding synchronizing circuits and employing setup and hold time constraints further enhance robustness against race conditions in sequential logic systems.

Solutions to Mitigate Hold State Issues

To mitigate hold state issues caused by race-around conditions in flip-flops, designers often implement edge-triggered flip-flops instead of level-triggered ones, ensuring state changes occur only at clock edges. Using master-slave flip-flop configurations effectively eliminates the race condition by separating input evaluation and state holding phases within the clock cycle. Introducing setup and hold time constraints alongside synchronized clock domains further reduces the risk of metastability and improves overall system reliability.

Real-World Examples and Case Studies

Race-around condition frequently appears in JK flip-flops operating in high-frequency clock environments, causing output oscillation and erroneous data states in digital circuits such as counters in microprocessors. Hold state issues are observed in complex pipelined processors like Intel's Pentium series, where failure to meet hold time constraints leads to metastability and data corruption during instruction execution. Case studies from digital system designs reveal that race conditions often necessitate synchronization techniques, while hold state problems drive the implementation of delay buffers and careful timing analysis to maintain signal integrity.

Best Practices for Reliable Circuit Design

To ensure reliable circuit design, avoid race-around conditions by using edge-triggered flip-flops instead of level-sensitive latches, which prevents unintended state changes when inputs switch simultaneously. Implementing proper synchronization and timing constraints guarantees that circuits do not enter hold states, maintaining signal integrity and stable data storage. You should also employ setup and hold time analysis during timing verification to optimize circuit performance and prevent data corruption.

Race-around condition vs hold state Infographic

electrown.com

electrown.com