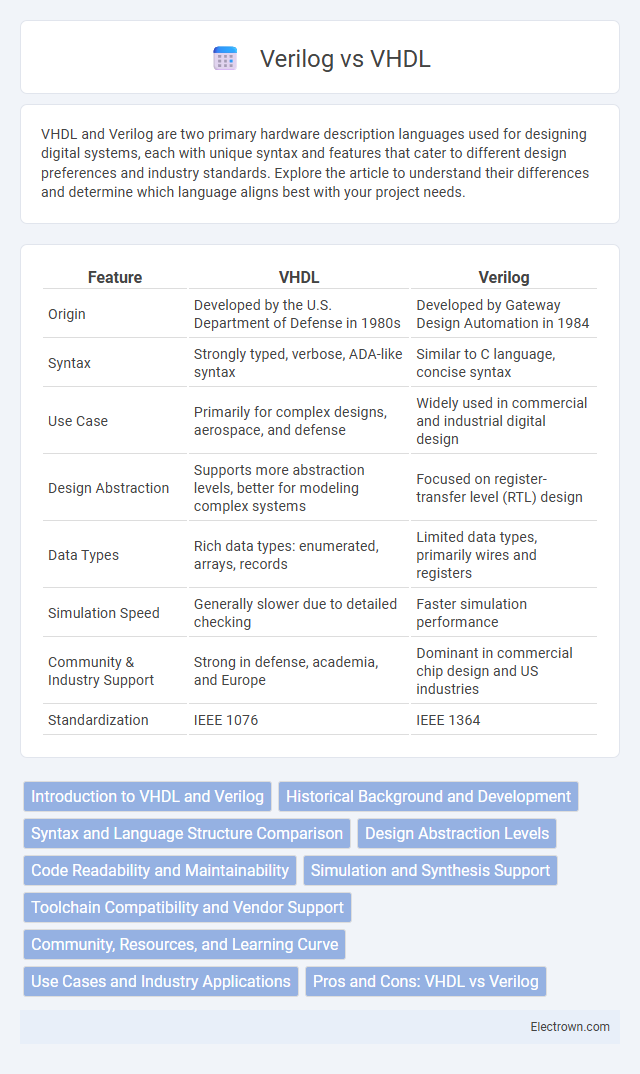

VHDL and Verilog are two primary hardware description languages used for designing digital systems, each with unique syntax and features that cater to different design preferences and industry standards. Explore the article to understand their differences and determine which language aligns best with your project needs.

Table of Comparison

| Feature | VHDL | Verilog |

|---|---|---|

| Origin | Developed by the U.S. Department of Defense in 1980s | Developed by Gateway Design Automation in 1984 |

| Syntax | Strongly typed, verbose, ADA-like syntax | Similar to C language, concise syntax |

| Use Case | Primarily for complex designs, aerospace, and defense | Widely used in commercial and industrial digital design |

| Design Abstraction | Supports more abstraction levels, better for modeling complex systems | Focused on register-transfer level (RTL) design |

| Data Types | Rich data types: enumerated, arrays, records | Limited data types, primarily wires and registers |

| Simulation Speed | Generally slower due to detailed checking | Faster simulation performance |

| Community & Industry Support | Strong in defense, academia, and Europe | Dominant in commercial chip design and US industries |

| Standardization | IEEE 1076 | IEEE 1364 |

Introduction to VHDL and Verilog

VHDL (VHSIC Hardware Description Language) and Verilog are the primary hardware description languages used for digital circuit design and FPGA programming. VHDL is strongly typed and emphasizes design clarity and documentation, making it suitable for complex, safety-critical applications. Verilog offers simpler syntax and faster simulation speed, often preferred for rapid prototyping and industry-standard ASIC design workflows.

Historical Background and Development

VHDL originated in the early 1980s, developed by the U.S. Department of Defense to standardize ASIC design documentation and simulation, emphasizing strong typing and modularity. Verilog, created by Gateway Design Automation in 1984, gained popularity for its simpler syntax and faster simulation performance, becoming an IEEE standard in 1995. Both languages evolved through industry collaboration, with VHDL favored in aerospace and defense, while Verilog dominated commercial ASIC and FPGA design.

Syntax and Language Structure Comparison

VHDL features a strongly typed, verbose syntax with extensive use of keywords and descriptive statements, promoting clarity and strict design verification. Verilog offers a more concise, C-like syntax with simpler data types and less verbosity, enabling faster prototyping and easier learning curves. The structural differences affect simulation speed, code readability, and tool compatibility in digital circuit design workflows.

Design Abstraction Levels

VHDL and Verilog support multiple design abstraction levels, including behavioral, register-transfer level (RTL), and gate level, enabling detailed hardware modeling and simulation. VHDL's strong typing and modular structure provide precise control at higher abstraction levels, while Verilog offers simplicity and efficiency, especially at the RTL level. Understanding these abstraction differences helps you optimize hardware design workflows and achieve accurate synthesis results.

Code Readability and Maintainability

VHDL offers stronger typing and verbose syntax, which enhances code readability and helps prevent errors, making it easier for teams to maintain complex designs over time. Verilog's concise syntax can speed up initial development but may introduce ambiguities, potentially complicating long-term maintenance and debugging efforts. Your choice between VHDL and Verilog should consider the balance between readability requirements and development speed to ensure sustainable project management.

Simulation and Synthesis Support

VHDL offers strong simulation capabilities with strict typing and powerful error checking, making it ideal for complex designs that require precise behavior verification. Verilog excels in synthesis support due to its simpler syntax and widespread industry adoption, facilitating efficient hardware implementation and faster design iteration. Your choice between VHDL and Verilog depends on whether you prioritize detailed simulation accuracy or streamlined synthesis workflows.

Toolchain Compatibility and Vendor Support

VHDL offers broad toolchain compatibility with major FPGA vendors such as Xilinx, Intel (Altera), and Microsemi, ensuring robust synthesis and simulation across diverse platforms. Verilog benefits from strong vendor support particularly in ASIC design flows, favored by companies like Cadence, Synopsys, and Mentor Graphics, enhancing integration in chip development ecosystems. Both languages maintain extensive IDE and third-party tool support, but VHDL's rigorous typing system often aligns better with military and aerospace toolchains, while Verilog's simplicity accelerates prototyping in commercial applications.

Community, Resources, and Learning Curve

VHDL boasts a strong presence in aerospace and defense industries with extensive documentation and a conservative, strongly-typed syntax that appeals to engineers focused on reliability, resulting in a steeper learning curve compared to Verilog. Verilog, favored in the commercial and ASIC design sectors, benefits from a larger, more active open-source community and abundant tutorials that facilitate easier onboarding for beginners. Resources such as vendor-specific tool support are robust for both languages, but Verilog's simplicity accelerates learning, while VHDL's verbosity demands more time to master thorough design principles.

Use Cases and Industry Applications

VHDL is widely used in aerospace, defense, and safety-critical systems due to its strong typing and rigorous syntax, ensuring high reliability in complex designs. Verilog dominates commercial semiconductor industries such as consumer electronics and communication devices because of its simplicity and faster simulation capabilities. Your choice between VHDL and Verilog depends on the project requirements and industry standards, as both languages excel in FPGA and ASIC design applications.

Pros and Cons: VHDL vs Verilog

VHDL offers strong typing and extensive syntax, promoting design reliability and clarity but often results in longer development times compared to Verilog. Verilog's simpler syntax and widespread use in industry allow faster prototyping and easier integration with existing IP cores, though it can lead to less strict type checking and potential design errors. Both languages support FPGA and ASIC development, with VHDL favored in defense and aerospace sectors, while Verilog is more common in commercial and high-speed digital designs.

VHDL vs Verilog Infographic

electrown.com

electrown.com