Hard macroeconomics focuses on quantifiable data such as GDP growth, inflation rates, and unemployment figures to analyze economic performance, while soft macroeconomics examines qualitative factors like consumer confidence and policy impacts on market sentiment. Understanding these distinctions can help you better navigate economic trends--read on to explore how each approach shapes economic insights.

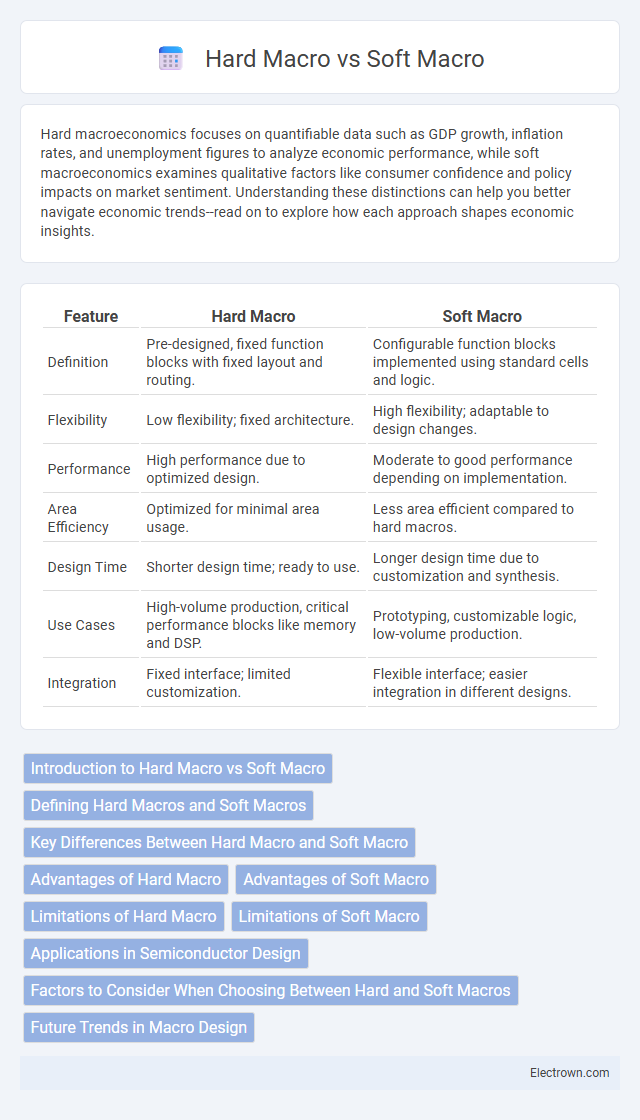

Table of Comparison

| Feature | Hard Macro | Soft Macro |

|---|---|---|

| Definition | Pre-designed, fixed function blocks with fixed layout and routing. | Configurable function blocks implemented using standard cells and logic. |

| Flexibility | Low flexibility; fixed architecture. | High flexibility; adaptable to design changes. |

| Performance | High performance due to optimized design. | Moderate to good performance depending on implementation. |

| Area Efficiency | Optimized for minimal area usage. | Less area efficient compared to hard macros. |

| Design Time | Shorter design time; ready to use. | Longer design time due to customization and synthesis. |

| Use Cases | High-volume production, critical performance blocks like memory and DSP. | Prototyping, customizable logic, low-volume production. |

| Integration | Fixed interface; limited customization. | Flexible interface; easier integration in different designs. |

Introduction to Hard Macro vs Soft Macro

Hard macro refers to pre-designed, fixed-layout circuit blocks with specific functionalities embedded in semiconductor chips, ensuring consistent performance and reduced design time. Soft macro consists of synthesizable RTL code or generic logic descriptions that enable flexible customization during the design process but require additional synthesis and place-and-route efforts. Understanding the differences between hard and soft macros is critical for optimizing chip design workflows, balancing performance, area, and time-to-market constraints.

Defining Hard Macros and Soft Macros

Hard macros are predefined, fixed hardware components or functions embedded directly into a semiconductor chip, providing consistent performance and efficiency. Soft macros refer to configurable, HDL-based intellectual property blocks that can be modified or synthesized according to your design requirements, offering flexibility during chip development. Understanding the distinctions between hard and soft macros helps optimize system design for performance, area, and power consumption.

Key Differences Between Hard Macro and Soft Macro

Hard macros are pre-designed, fully verified circuit blocks embedded in an integrated circuit to perform specific functions, offering fixed functionality and optimized performance. Soft macros consist of synthesizable RTL code that can be customized and adapted by designers, providing flexibility in design and integration within various technologies. Key differences include hard macros' fixed layout and timing, contrasting with soft macros' flexibility and dependency on synthesis and place-and-route tools for implementation.

Advantages of Hard Macro

Hard macros provide reliable, pre-designed circuit blocks with optimized layout and timing, ensuring consistent performance in your integrated circuit designs. Their fixed physical structures reduce design time and simplify verification compared to soft macros, which require customization and optimization. Utilizing hard macros enhances silicon efficiency and helps meet stringent power, area, and speed requirements in complex chip development.

Advantages of Soft Macro

Soft macros offer significant flexibility by allowing users to easily modify and customize macro code without altering physical hardware, making them ideal for diverse application requirements. They enable rapid prototyping and debugging within design environments, reducing development time and costs compared to hard macros that require fixed, pre-verified logic blocks. The reusability of soft macros across multiple projects enhances scalability and supports iterative improvements in FPGA and ASIC designs.

Limitations of Hard Macro

Hard macros have fixed functionality and layout, which limits design flexibility and adaptability to changing requirements. They consume more silicon area and often result in suboptimal performance compared to soft macros that can be customized and optimized during synthesis. Your design may face integration challenges and reduced scalability when relying heavily on hard macros.

Limitations of Soft Macro

Soft macros are limited by their dependence on software interpretation, which often results in slower execution speeds compared to hard macros embedded in hardware. They are more prone to variations in performance due to processor load and system resource constraints. The flexibility of soft macros comes at the cost of reduced reliability and precision, making them less suitable for timing-critical or high-frequency operations.

Applications in Semiconductor Design

Hard macros in semiconductor design offer fixed, pre-verified circuit blocks with optimized performance and predictable timing, ideal for high-speed and power-sensitive applications such as CPUs and memory arrays. Soft macros provide flexible, synthesizable RTL descriptions that enable customization and scalability, making them suitable for FPGA designs and early-stage ASIC prototyping. Integrating hard macros reduces design risk and accelerates tape-out schedules, while soft macros enhance design adaptability and post-silicon revisions.

Factors to Consider When Choosing Between Hard and Soft Macros

Choosing between hard macros and soft macros depends on design flexibility, performance requirements, and area constraints. Hard macros offer fixed layouts with optimized speed and power, making them suitable for critical paths in ASIC design, while soft macros provide adaptability and scalability due to their synthesizable nature. Evaluating trade-offs between customization capability and predictable implementation helps determine the appropriate macro type for a specific semiconductor project.

Future Trends in Macro Design

Future trends in macro design emphasize the integration of AI-driven automation to enhance both hard macro precision and soft macro flexibility. Hard macros will evolve with increased standardization and optimization for high-performance silicon chips, while soft macros will benefit from improved configurability and adaptive algorithms to meet diverse design needs. You can expect hybrid solutions to emerge, combining the reliability of hard macros with the versatility of soft macros for innovative semiconductor applications.

Hard Macro vs Soft Macro Infographic

electrown.com

electrown.com