Source-coupled logic (SCL) offers lower noise and higher speed by using transistors connected at the source, while drain-coupled logic (DCL) typically provides simpler circuit design with better voltage swing through transistor connections at the drain. Exploring the trade-offs between speed, noise, and complexity in these logic styles will help you choose the best approach for your digital circuit designs; read on to delve deeper into their comparative analysis.

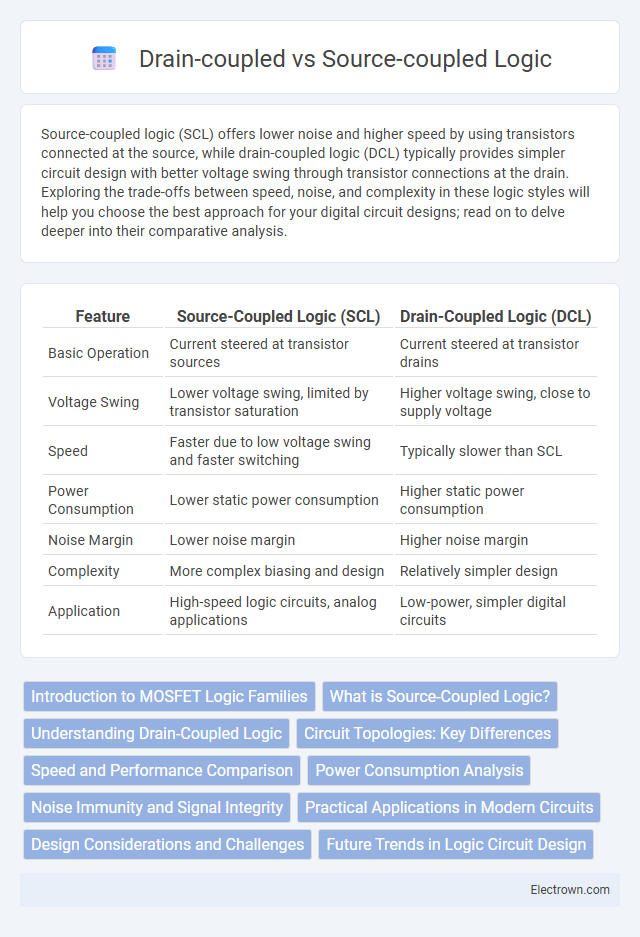

Table of Comparison

| Feature | Source-Coupled Logic (SCL) | Drain-Coupled Logic (DCL) |

|---|---|---|

| Basic Operation | Current steered at transistor sources | Current steered at transistor drains |

| Voltage Swing | Lower voltage swing, limited by transistor saturation | Higher voltage swing, close to supply voltage |

| Speed | Faster due to low voltage swing and faster switching | Typically slower than SCL |

| Power Consumption | Lower static power consumption | Higher static power consumption |

| Noise Margin | Lower noise margin | Higher noise margin |

| Complexity | More complex biasing and design | Relatively simpler design |

| Application | High-speed logic circuits, analog applications | Low-power, simpler digital circuits |

Introduction to MOSFET Logic Families

MOSFET logic families include source-coupled and drain-coupled logic circuits, which differ primarily in the connection points of their loads and current sources. Source-coupled logic (SCL) typically uses a current source connected to the source terminals of MOSFETs, resulting in faster switching speeds and lower voltage swings suitable for high-speed applications. Drain-coupled logic (DCL) connects the load at the drain terminals, offering simpler design but generally higher power consumption and lower frequency performance compared to source-coupled logic.

What is Source-Coupled Logic?

Source-Coupled Logic (SCL) is a high-speed digital logic family that utilizes bipolar junction transistors (BJTs) with current steering between two branches sharing a common current source at the transistor sources. This topology enables low voltage swings and fast switching speeds, ideal for high-frequency applications and minimizing power consumption compared to traditional logic families. Your design benefits from SCL's enhanced noise immunity and robust performance in integrated circuits that require precise timing and low power dissipation.

Understanding Drain-Coupled Logic

Drain-coupled logic (DCL) is a high-speed digital logic family used in integrated circuits, where the logic gates share a common drain node connected to a current source, enhancing switching speed and reducing power dissipation. This configuration offers improved noise margins and faster transition times compared to source-coupled logic (SCL), making DCL especially suitable for high-frequency applications like radio-frequency (RF) circuits and digital signal processing. Understanding your circuit's requirements will help determine if drain-coupled logic's benefits in speed and power efficiency outweigh its design complexity.

Circuit Topologies: Key Differences

Source-coupled logic (SCL) employs a current source connected to the sources of transistors, offering high-speed operation with reduced voltage swing, while drain-coupled logic (DCL) uses resistive loads connected to transistor drains, resulting in larger voltage swings but simpler circuit design. SCL topologies provide better noise margins and lower power consumption due to constant current biasing, whereas DCL circuits often exhibit higher output voltage levels but increased power dissipation. Your choice between these circuit topologies depends on trade-offs in speed, power efficiency, and noise immunity requirements for the application.

Speed and Performance Comparison

Source-coupled logic (SCL) typically offers faster switching speeds and lower delay due to its current steering mechanism, which enables quicker signal transitions compared to drain-coupled logic (DCL). Drain-coupled logic often experiences higher parasitic capacitances and slower response times, resulting in reduced overall performance for high-frequency applications. Your choice between SCL and DCL should consider the required speed and power trade-offs, with SCL generally preferred for high-speed, low-voltage integrated circuits.

Power Consumption Analysis

Source-coupled logic (SCL) demonstrates lower power consumption compared to drain-coupled logic (DCL) due to its constant current biasing, which reduces dynamic power dissipation. In DCL, varying current levels lead to increased switching power and higher energy usage, making it less efficient for power-sensitive applications. Your choice between SCL and DCL should consider these differences to optimize energy efficiency in high-speed digital circuits.

Noise Immunity and Signal Integrity

Source-coupled logic (SCL) typically exhibits superior noise immunity and signal integrity due to its differential architecture, which effectively rejects common-mode noise and reduces signal distortion. Drain-coupled logic (DCL), while simpler, is more susceptible to voltage fluctuations and cross-talk, leading to potential signal degradation in high-speed or noisy environments. Your choice between SCL and DCL impacts circuit robustness, with SCL preferred for applications demanding high noise resilience and stable signal quality.

Practical Applications in Modern Circuits

Source-coupled logic (SCL) is widely used in high-speed digital circuits requiring low noise and fast switching, such as in communication systems and clock distribution networks due to its differential signaling and improved signal integrity. Drain-coupled logic (DCL) finds practical applications in analog and mixed-signal designs where moderate speed with lower power consumption is essential, including data converters and integrated RF circuits. Both logic styles optimize performance in modern circuits by balancing speed, power efficiency, and noise immunity specific to their operational environments.

Design Considerations and Challenges

Source-coupled logic (SCL) offers higher speed and better noise immunity due to its current-mode operation but requires precise biasing and careful layout to minimize device mismatch and improve common-mode rejection. Drain-coupled logic (DCL) generally simplifies biasing and reduces voltage headroom challenges but suffers from slower switching speeds and increased susceptibility to noise because of its voltage-mode operation. Designers must balance speed, power consumption, noise margin, and fabrication variability when choosing between SCL and DCL for high-frequency, low-power digital circuits.

Future Trends in Logic Circuit Design

Future trends in logic circuit design emphasize improved speed and power efficiency, with source-coupled logic (SCL) gaining traction for its lower noise and faster switching capabilities compared to drain-coupled logic (DCL). Innovations in nanotechnology and material science are driving the adoption of SCL in high-frequency applications, enhancing signal integrity and reducing power consumption. Your choice between SCL and DCL will increasingly depend on balancing performance needs with design complexity in emerging semiconductor technologies.

Source-coupled vs Drain-coupled logic Infographic

electrown.com

electrown.com