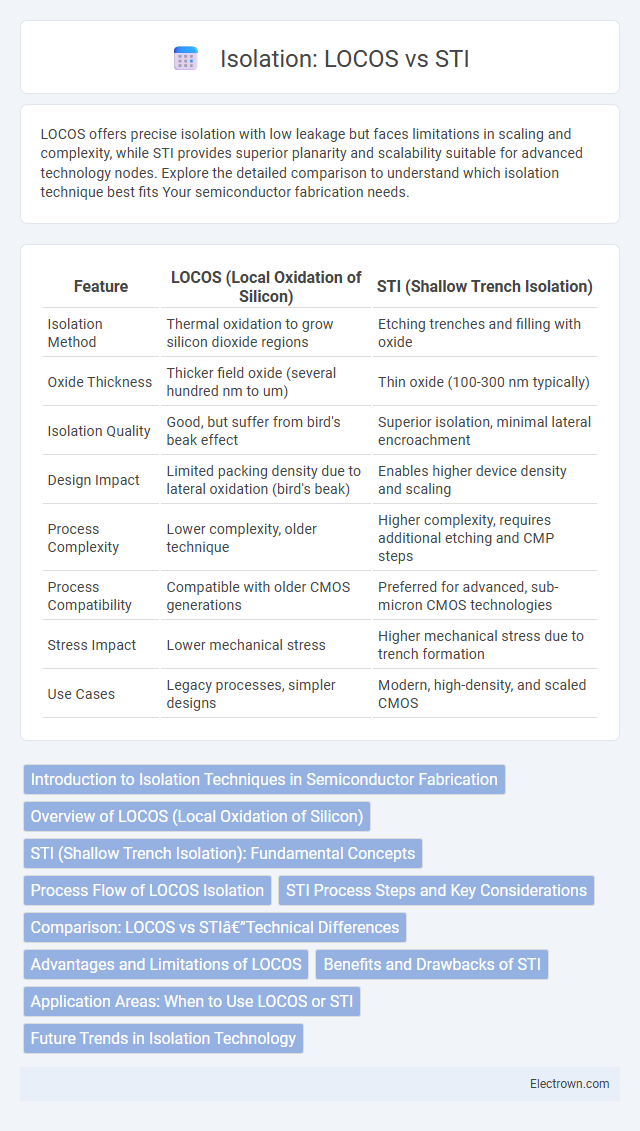

LOCOS offers precise isolation with low leakage but faces limitations in scaling and complexity, while STI provides superior planarity and scalability suitable for advanced technology nodes. Explore the detailed comparison to understand which isolation technique best fits Your semiconductor fabrication needs.

Table of Comparison

| Feature | LOCOS (Local Oxidation of Silicon) | STI (Shallow Trench Isolation) |

|---|---|---|

| Isolation Method | Thermal oxidation to grow silicon dioxide regions | Etching trenches and filling with oxide |

| Oxide Thickness | Thicker field oxide (several hundred nm to um) | Thin oxide (100-300 nm typically) |

| Isolation Quality | Good, but suffer from bird's beak effect | Superior isolation, minimal lateral encroachment |

| Design Impact | Limited packing density due to lateral oxidation (bird's beak) | Enables higher device density and scaling |

| Process Complexity | Lower complexity, older technique | Higher complexity, requires additional etching and CMP steps |

| Process Compatibility | Compatible with older CMOS generations | Preferred for advanced, sub-micron CMOS technologies |

| Stress Impact | Lower mechanical stress | Higher mechanical stress due to trench formation |

| Use Cases | Legacy processes, simpler designs | Modern, high-density, and scaled CMOS |

Introduction to Isolation Techniques in Semiconductor Fabrication

Isolation techniques in semiconductor fabrication are critical for preventing electrical interference between adjacent devices on a chip. LOCOS (Local Oxidation of Silicon) creates isolation by growing a thick oxide layer locally, while STI (Shallow Trench Isolation) involves etching shallow trenches filled with dielectric material for improved planarization and device scaling. STI has become the preferred method for advanced nodes due to its superior scalability, reduced parasitic capacitance, and compatibility with high-density integration.

Overview of LOCOS (Local Oxidation of Silicon)

Local Oxidation of Silicon (LOCOS) is a widely used technique for device isolation in semiconductor fabrication, involving the selective oxidation of silicon areas to create insulating silicon dioxide regions. The process utilizes a silicon nitride mask to protect active regions while allowing thermal oxidation in exposed areas, forming a field oxide that electrically isolates individual transistors. Despite its simplicity and reliability, LOCOS faces challenges such as the "bird's beak" effect, which limits scaling and device density in advanced CMOS technologies.

STI (Shallow Trench Isolation): Fundamental Concepts

Shallow Trench Isolation (STI) is a semiconductor fabrication technique used to electrically isolate transistors in integrated circuits by etching shallow trenches into the silicon substrate and filling them with dielectric materials like silicon dioxide. Compared to Local Oxidation of Silicon (LOCOS), STI offers superior planarization, reduced device size, and minimized parasitic capacitance, enabling higher transistor density and improved performance. STI's precise trench formation and liner oxidation processes are critical for preventing substrate damage and ensuring reliable isolation in advanced CMOS technologies.

Process Flow of LOCOS Isolation

The process flow of LOCOS (Local Oxidation of Silicon) isolation begins with the deposition of a thin silicon nitride layer acting as an oxidation mask, followed by thermally growing a thick silicon dioxide field oxide where the silicon is exposed. The silicon nitride layer prevents oxidation in the active regions, ensuring electrical isolation between devices. Finally, the nitride is removed, and planarization steps are applied to prepare the wafer surface for subsequent device fabrication.

STI Process Steps and Key Considerations

The Shallow Trench Isolation (STI) process involves etching narrow trenches into the silicon substrate, filling them with dielectric material such as silicon dioxide, and then planarizing the surface using Chemical Mechanical Polishing (CMP) to achieve a smooth, flat wafer surface. Key considerations in STI include controlling trench depth and width to prevent stress-induced defects and ensuring proper oxide fill to avoid voids or seams that could compromise device isolation. Your choice of STI parameters directly impacts device performance by minimizing parasitic capacitance and enhancing transistor reliability in advanced CMOS technologies.

Comparison: LOCOS vs STI—Technical Differences

LOCOS (Local Oxidation of Silicon) uses a thick field oxide grown through selective oxidation to isolate devices, resulting in bird's beak encroachment and limited scaling for advanced nodes. STI (Shallow Trench Isolation) employs etched trenches filled with dielectric material, offering superior planarization and reduced lateral oxidation effects, enabling finer device geometries and higher integration density. The technical differences between LOCOS and STI directly impact device performance, leakage currents, and manufacturing complexity in CMOS fabrication.

Advantages and Limitations of LOCOS

LOCOS (Local Oxidation of Silicon) offers advantages such as excellent planar isolation and reduced leakage currents due to the thick field oxide, which improves device reliability in analog and power applications. However, LOCOS faces limitations including the bird's beak effect that reduces active area, increased process complexity, and difficulty scaling for submicron technologies compared to Shallow Trench Isolation (STI). These drawbacks limit LOCOS efficiency in modern integrated circuits requiring high-density scaling and precise isolation profiles.

Benefits and Drawbacks of STI

Shallow Trench Isolation (STI) offers precise isolation and supports higher device density compared to Local Oxidation of Silicon (LOCOS), enabling better scalability for advanced CMOS technologies. STI reduces the bird's beak effect found in LOCOS, minimizing active area loss and improving silicon area utilization, which is critical for smaller geometries. However, STI can introduce stress-induced defects near trench edges, potentially affecting transistor performance and reliability, requiring careful process optimization.

Application Areas: When to Use LOCOS or STI

LOCOS (Local Oxidation of Silicon) isolation is ideal for analog and high-voltage circuits requiring thick field oxide for better isolation, while STI (Shallow Trench Isolation) is preferred in high-density CMOS digital circuits due to its superior planarity and reduced parasitic capacitance. You should choose LOCOS in applications where minimizing leakage current and high-quality isolation are critical, especially in RF and power devices. STI is more suitable for advanced CMOS processes demanding precise device scaling and high integration density, such as microprocessors and memory circuits.

Future Trends in Isolation Technology

Future trends in isolation technology emphasize the shift from LOCOS (Local Oxidation of Silicon) to STI (Shallow Trench Isolation) due to STI's superior scalability and reduced device parasitic capacitance in advanced semiconductor nodes. With the increasing demand for higher transistor density and improved device performance in sub-7nm technologies, STI provides enhanced planarization and better isolation precision, supporting aggressive scaling requirements. Ensuring your semiconductor fabrication process adopts STI innovations can optimize integration density and reliability for next-generation IC manufacturing.

Isolation: LOCOS vs STI Infographic

electrown.com

electrown.com