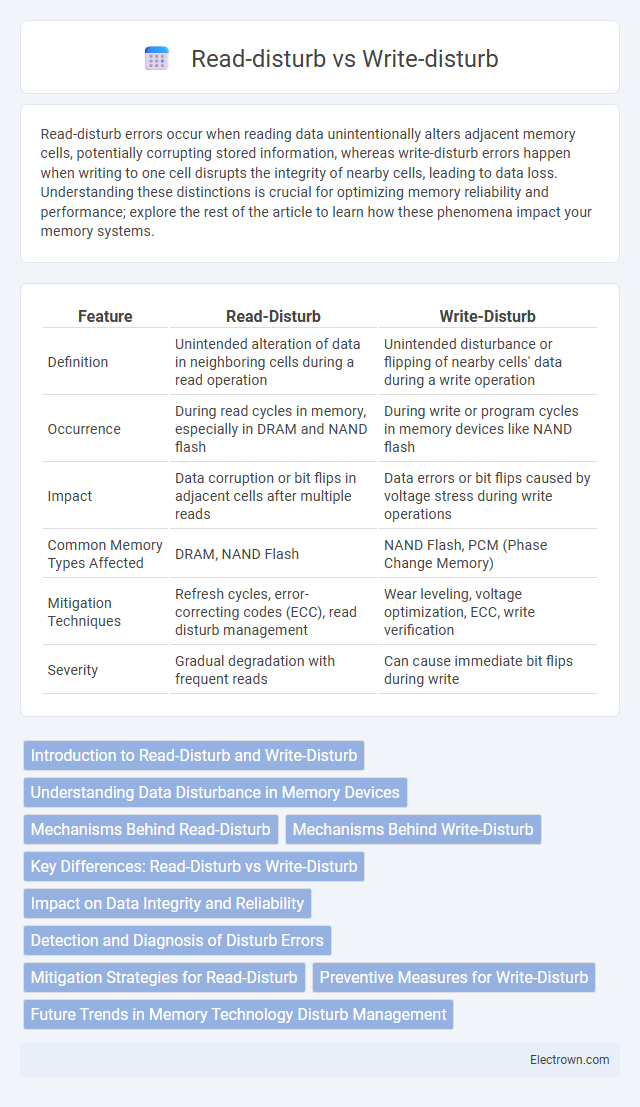

Read-disturb errors occur when reading data unintentionally alters adjacent memory cells, potentially corrupting stored information, whereas write-disturb errors happen when writing to one cell disrupts the integrity of nearby cells, leading to data loss. Understanding these distinctions is crucial for optimizing memory reliability and performance; explore the rest of the article to learn how these phenomena impact your memory systems.

Table of Comparison

| Feature | Read-Disturb | Write-Disturb |

|---|---|---|

| Definition | Unintended alteration of data in neighboring cells during a read operation | Unintended disturbance or flipping of nearby cells' data during a write operation |

| Occurrence | During read cycles in memory, especially in DRAM and NAND flash | During write or program cycles in memory devices like NAND flash |

| Impact | Data corruption or bit flips in adjacent cells after multiple reads | Data errors or bit flips caused by voltage stress during write operations |

| Common Memory Types Affected | DRAM, NAND Flash | NAND Flash, PCM (Phase Change Memory) |

| Mitigation Techniques | Refresh cycles, error-correcting codes (ECC), read disturb management | Wear leveling, voltage optimization, ECC, write verification |

| Severity | Gradual degradation with frequent reads | Can cause immediate bit flips during write |

Introduction to Read-Disturb and Write-Disturb

Read-disturb occurs when repeated read operations cause unintended changes or errors in neighboring memory cells, potentially leading to data corruption. Write-disturb refers to the unintended alteration of data in adjacent cells during write operations, often caused by electrical interference or voltage stress. Understanding these disturbances is crucial for improving the reliability and longevity of memory devices in your digital systems.

Understanding Data Disturbance in Memory Devices

Data disturbance in memory devices primarily involves read-disturb and write-disturb phenomena, where repeated read or write operations unintentionally alter adjacent memory cells' stored data. Read-disturb occurs due to repeated access causing threshold voltage shifts in nearby cells, while write-disturb happens when high-voltage programming disturbs neighboring cell states. Understanding these disturbances helps you design more reliable memory management techniques and error correction methods to preserve data integrity in non-volatile memory technologies like NAND flash and DRAM.

Mechanisms Behind Read-Disturb

Read-disturb occurs when repeated reading of a memory cell inadvertently alters the charge in adjacent cells, leading to data corruption over time, primarily in NAND flash memory. This phenomenon stems from the physical coupling and electrical interference during the read operation, where the high voltage applied can disturb neighboring cells' stored charges. Understanding the mechanisms behind read-disturb helps you implement error correction techniques and optimize memory management to mitigate data loss.

Mechanisms Behind Write-Disturb

Write-disturb errors occur when writing data to a memory cell inadvertently alters the charge of adjacent cells, leading to data corruption. This phenomenon arises from parasitic capacitance and electrical interference during the write operation, causing a disturbance in neighboring cells' stored charges. Understanding these mechanisms is crucial to mitigate errors and improve the reliability of your memory devices compared to read-disturb, which primarily results from repeated read operations causing data degradation.

Key Differences: Read-Disturb vs Write-Disturb

Read-disturb occurs when repeatedly reading data from memory cells inadvertently alters the stored information in adjacent cells, while write-disturb happens during the write operation where unintended changes can affect neighboring cells. Read-disturb is primarily associated with the cumulative stress from frequent accesses without data modification, whereas write-disturb arises due to voltage-induced interference during programming. Understanding these differences is crucial for designing error mitigation strategies in non-volatile memory technologies such as NAND flash and DRAM.

Impact on Data Integrity and Reliability

Read-disturb errors occur when repeated read operations inadvertently alter stored data, leading to gradual corruption in high-density memory like DRAM and NAND flash. Write-disturb errors arise during write operations, where adjacent memory cells are unintentionally modified, compromising data integrity and causing unreliable storage in technologies such as NAND flash memory. Both phenomena degrade data reliability by increasing the risk of bit errors, necessitating robust error correction codes (ECC) and memory management techniques to maintain system stability.

Detection and Diagnosis of Disturb Errors

Detection and diagnosis of read-disturb errors typically involve monitoring unexpected bit flips in memory cells that remain unaltered by direct write operations, using error correction codes (ECC) and retention tests to identify subtle decay caused by frequent reads. Write-disturb errors are diagnosed by analyzing interference patterns during write operations, where neighboring cells experience voltage fluctuations, often detected through stress testing and write cycling coupled with specialized debugging tools to pinpoint affected regions. Your memory system's robustness can be significantly improved by integrating advanced machine learning algorithms that predict and classify disturb errors, enabling proactive error mitigation strategies.

Mitigation Strategies for Read-Disturb

Mitigation strategies for read-disturb errors primarily involve error-correcting codes (ECC) and refresh mechanisms that periodically rewrite data to prevent bit flips caused by repeated reads in NAND flash memory. Advanced wear-leveling algorithms and adaptive read voltage tuning also play crucial roles in minimizing read-disturb effects by distributing read operations evenly and optimizing threshold voltage levels. Techniques like blacklisting vulnerable blocks and employing robust data management policies further enhance endurance and reliability in NAND-based storage systems.

Preventive Measures for Write-Disturb

Preventive measures for write-disturb in memory devices include implementing error correction codes (ECC) and wear leveling techniques to evenly distribute write operations. Utilizing advanced write algorithms that minimize voltage stress and employing shielding technologies can further reduce the risk of unintended data alteration. Regular monitoring of memory cell health and adaptive refresh cycles help maintain data integrity by mitigating write-disturb effects.

Future Trends in Memory Technology Disturb Management

Future trends in memory technology emphasize advanced algorithms and error-correcting codes to mitigate read-disturb and write-disturb effects in high-density non-volatile memories such as NAND flash and emerging Resistive RAM (ReRAM). Machine learning techniques are increasingly applied to predict and prevent disturbance-induced failures, enhancing data integrity and device longevity. Innovations in materials and cell architecture aim to reduce susceptibility to disturbances, supporting reliable storage in next-generation memory systems.

Read-disturb vs Write-disturb Infographic

electrown.com

electrown.com