Edge triggered flip-flops capture data only at specific clock pulse transitions, offering precise timing control and reducing the chance of glitches in digital circuits. Understanding the differences between these and level triggered flip-flops can enhance Your ability to design efficient sequential logic, so explore the article to learn more.

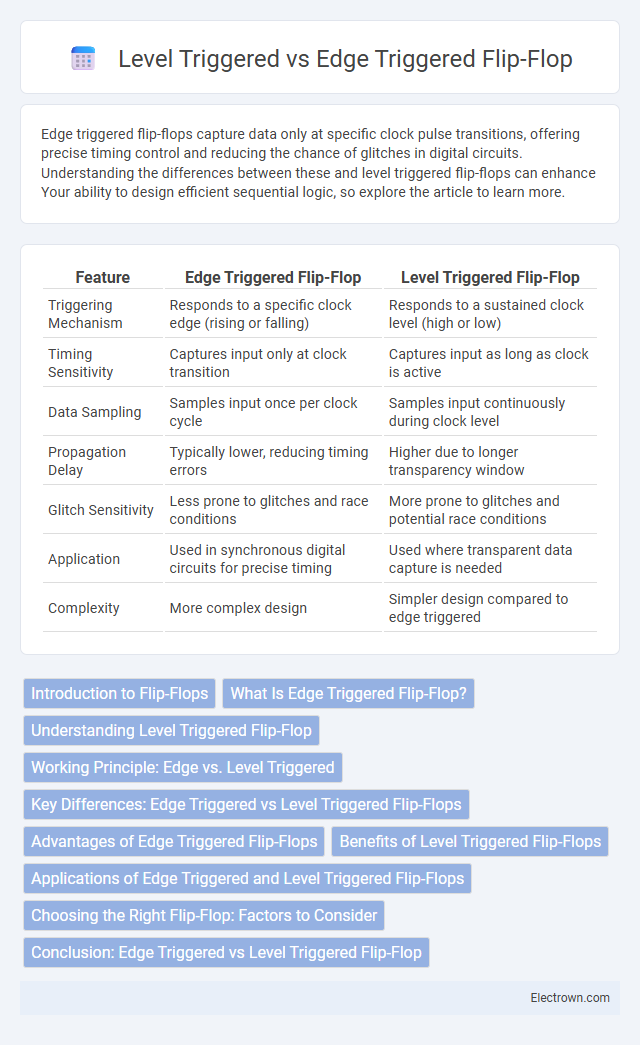

Table of Comparison

| Feature | Edge Triggered Flip-Flop | Level Triggered Flip-Flop |

|---|---|---|

| Triggering Mechanism | Responds to a specific clock edge (rising or falling) | Responds to a sustained clock level (high or low) |

| Timing Sensitivity | Captures input only at clock transition | Captures input as long as clock is active |

| Data Sampling | Samples input once per clock cycle | Samples input continuously during clock level |

| Propagation Delay | Typically lower, reducing timing errors | Higher due to longer transparency window |

| Glitch Sensitivity | Less prone to glitches and race conditions | More prone to glitches and potential race conditions |

| Application | Used in synchronous digital circuits for precise timing | Used where transparent data capture is needed |

| Complexity | More complex design | Simpler design compared to edge triggered |

Introduction to Flip-Flops

Flip-flops are fundamental digital memory elements used to store binary data with two stable states, labeled as 0 and 1. They operate based on clock signals, with edge triggered flip-flops responding to clock transitions (rising or falling edges) and level triggered flip-flops responding to the clock signal level (high or low). The distinction between edge triggered and level triggered behavior is critical for timing accuracy and synchronization in sequential digital circuits.

What Is Edge Triggered Flip-Flop?

An edge-triggered flip-flop captures input data precisely at the transition edge of the clock signal, either on the rising or falling edge, enabling synchronized data storage in digital circuits. This type of flip-flop improves timing accuracy by responding only during the clock edge, minimizing glitches that occur during stable clock levels. Commonly used in sequential logic design, edge-triggered flip-flops ensure reliable state changes aligned with clock pulses.

Understanding Level Triggered Flip-Flop

Level triggered flip-flops respond to the input data as long as the clock signal remains at a specific logic level (either high or low), allowing continuous data flow during that interval. This characteristic can lead to transparency issues and potential glitches because the output directly follows the input while the clock level is active. Engineers often use level triggered flip-flops in applications where data stability isn't critical during the clock period, contrasting with edge triggered flip-flops that capture input only at clock transitions for precise timing control.

Working Principle: Edge vs. Level Triggered

Edge triggered flip-flops capture input data only at the transition or edge of the clock signal, either on the rising or falling edge, ensuring precise timing control in digital circuits. Level triggered flip-flops respond to the input while the clock signal remains at a specific level, typically high or low, which can lead to multiple data captures during the clock pulse. Understanding these working principles helps you select the appropriate flip-flop type for synchronization and timing accuracy in your digital design.

Key Differences: Edge Triggered vs Level Triggered Flip-Flops

Edge triggered flip-flops change their output state only at specific clock signal transitions, typically the rising or falling edge, ensuring precise timing control in digital circuits. Level triggered flip-flops, on the other hand, respond to the input signals as long as the clock is at a particular level, making them more sensitive to input changes during that period. Your choice between these flip-flop types affects timing accuracy and noise immunity in synchronous circuit designs.

Advantages of Edge Triggered Flip-Flops

Edge triggered flip-flops offer precise control by capturing input data only at specific clock edges, minimizing timing errors and improving circuit reliability. This characteristic allows them to synchronize operations efficiently in high-speed digital systems, reducing the risk of data corruption due to signal noise. Your designs benefit from improved timing accuracy and enhanced performance in sequential logic applications by using edge triggered flip-flops.

Benefits of Level Triggered Flip-Flops

Level triggered flip-flops provide greater flexibility in timing applications by maintaining their output state as long as the clock signal remains at a particular logic level. This characteristic allows for simpler design implementation and easier synchronization in digital circuits, reducing the risk of missing signal transitions. Your circuit benefits from improved stability and predictable behavior when using level triggered flip-flops in environments with slower or less stable clock signals.

Applications of Edge Triggered and Level Triggered Flip-Flops

Edge triggered flip-flops are predominantly used in synchronous circuits like digital registers and counters, where precise timing and clock synchronization are critical for capturing data at the exact moment of a clock edge. Level triggered flip-flops find application in asynchronous circuits and memory devices, providing stable data storage and transfer during the entire duration of the enable signal level. High-speed data processing systems favor edge triggered flip-flops for their ability to minimize timing hazards and reduce setup and hold time constraints.

Choosing the Right Flip-Flop: Factors to Consider

Choosing the right flip-flop depends on timing accuracy and circuit speed requirements, with edge-triggered flip-flops preferred for precise synchronization due to their response on clock transitions. Level-triggered flip-flops offer simpler designs for latches but may introduce glitches in high-speed applications. Your selection should consider power consumption, setup and hold times, and the complexity of your digital circuit environment.

Conclusion: Edge Triggered vs Level Triggered Flip-Flop

Edge triggered flip-flops capture input data only at specific clock transitions, offering precise timing control suitable for high-speed and synchronous circuits. Level triggered flip-flops respond to input signals as long as the clock level is active, which can lead to potential timing hazards like glitches or race conditions. Choosing between edge and level triggered flip-flops depends on the required timing accuracy, circuit complexity, and susceptibility to timing errors in digital system design.

Edge Triggered vs Level Triggered Flip-Flop Infographic

electrown.com

electrown.com