Blocking assignments execute statements sequentially, causing each operation to complete before the next begins, which can simplify debugging but may reduce simulation speed. Non-blocking assignments allow multiple operations to occur concurrently, improving performance and accurately modeling hardware behavior; explore the rest of the article to understand how each type impacts your Verilog design.

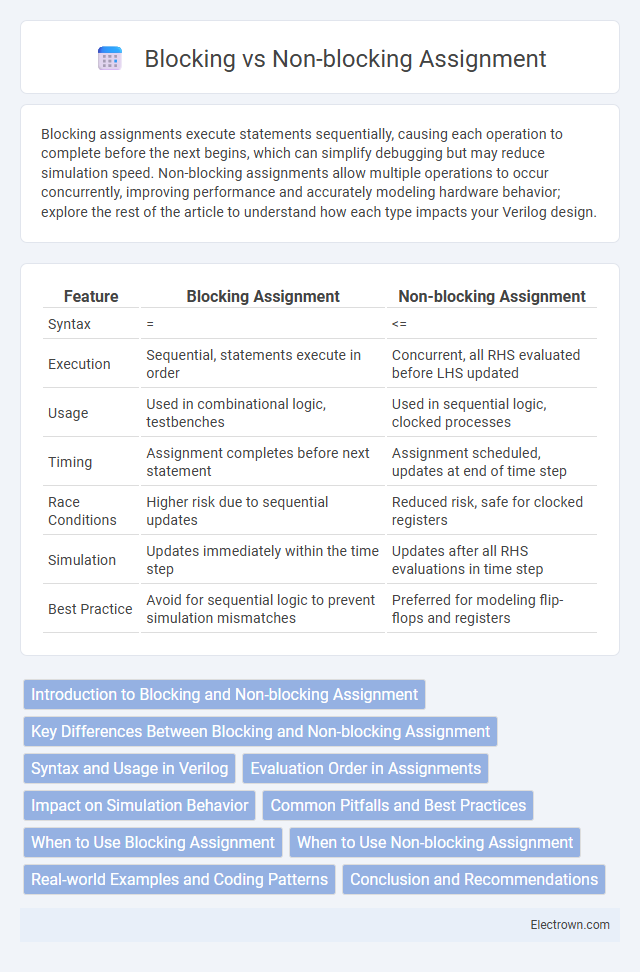

Table of Comparison

| Feature | Blocking Assignment | Non-blocking Assignment |

|---|---|---|

| Syntax | = | <= |

| Execution | Sequential, statements execute in order | Concurrent, all RHS evaluated before LHS updated |

| Usage | Used in combinational logic, testbenches | Used in sequential logic, clocked processes |

| Timing | Assignment completes before next statement | Assignment scheduled, updates at end of time step |

| Race Conditions | Higher risk due to sequential updates | Reduced risk, safe for clocked registers |

| Simulation | Updates immediately within the time step | Updates after all RHS evaluations in time step |

| Best Practice | Avoid for sequential logic to prevent simulation mismatches | Preferred for modeling flip-flops and registers |

Introduction to Blocking and Non-blocking Assignment

Blocking assignment in Verilog uses the "=" operator to execute statements sequentially within a procedural block, ensuring the current statement completes before the next begins. Non-blocking assignment, denoted by "<=", schedules the assignment to occur at the end of the current time step, allowing parallel execution of multiple statements. These fundamental differences are crucial in modeling combinational and sequential logic accurately in hardware design.

Key Differences Between Blocking and Non-blocking Assignment

Blocking assignment in hardware description languages like Verilog uses the "=" operator and executes statements sequentially, causing each assignment to complete before the next begins. Non-blocking assignment, denoted by "<=", schedules assignments to occur concurrently at the end of the current time step, allowing parallel execution essential for modeling flip-flop behavior. The key difference lies in execution order and timing: blocking assignments block subsequent statements until completion, while non-blocking assignments enable simultaneous updates, preventing race conditions in sequential logic.

Syntax and Usage in Verilog

Blocking assignments in Verilog use the "=" operator and evaluate statements sequentially within an always block, making them suitable for combinational logic. Non-blocking assignments employ the "<=" operator, allowing simultaneous updates by scheduling assignments to occur at the end of the current time step, which is essential for modeling synchronous sequential logic. Proper use of blocking and non-blocking assignments impacts simulation accuracy and hardware synthesis results.

Evaluation Order in Assignments

Blocking assignments in Verilog evaluate and execute sequentially in the exact order they are written, causing subsequent statements to wait until the current assignment completes. Non-blocking assignments allow all right-hand side expressions to be evaluated first, then update all the left-hand side variables simultaneously at the end of the current time step. Your choice between blocking and non-blocking affects simulation accuracy and timing behavior due to these fundamental differences in evaluation order.

Impact on Simulation Behavior

Blocking assignments execute sequentially within a simulation time step, causing dependent statements to wait for the current assignment to complete, which can slow down the simulation but provides predictable behavior. Non-blocking assignments update variables concurrently at the end of the time step, enabling more efficient simulation and parallelism in hardware modeling. The choice impacts timing accuracy, race conditions, and simulation performance, with non-blocking assignments preferred for sequential logic and blocking for combinational logic.

Common Pitfalls and Best Practices

Blocking assignments in Verilog use the "=" operator and execute statements sequentially, which can cause race conditions and simulation mismatches if misused in sequential logic. Non-blocking assignments, denoted by "<=", allow concurrent updates and are preferred for modeling synchronous logic to avoid timing inconsistencies and ensure predictable behavior. Best practices include using blocking assignments only for combinational logic and consistently applying non-blocking assignments in always blocks triggered by clock edges to prevent common pitfalls like unintended data overwrites and simulation-synthesis mismatches.

When to Use Blocking Assignment

Use blocking assignment in Verilog for combinational logic and situations where the order of operations is critical within an always block, enabling immediate updates of variables. It is ideal for modeling behaviors where statements must execute sequentially and each assignment depends on the completion of the previous one. Blocking assignments help prevent unintended race conditions in sequential procedural code by ensuring natural, step-by-step execution flow.

When to Use Non-blocking Assignment

Use non-blocking assignments in sequential logic within always blocks triggered by clock edges to model flip-flop behavior accurately. They allow multiple assignments to execute concurrently, preventing race conditions and ensuring correct simulation of hardware registers. Non-blocking assignments are essential when designing synchronous circuits to maintain timing consistency and proper data flow.

Real-world Examples and Coding Patterns

Blocking assignments in Verilog, denoted by '=', execute sequentially within an always block, making them suitable for combinational logic like multiplexers or simple arithmetic operations where order of evaluation is critical. Non-blocking assignments, indicated by '<=', allow parallel updates in sequential logic such as flip-flops and registers, preventing race conditions in clocked processes by updating values only at the end of the time step. Real-world coding patterns typically use blocking assignments for combinational circuits and non-blocking assignments for synchronous designs, ensuring accurate simulation and synthesis results.

Conclusion and Recommendations

Blocking assignments execute sequentially, causing your code to wait for each statement to complete, which can simplify debugging but may reduce simulation efficiency. Non-blocking assignments allow statements to execute concurrently, improving simulation speed and accurately modeling hardware behavior in sequential logic. For optimal design, use blocking assignments in combinational logic and non-blocking assignments in sequential logic to ensure clarity and reliable timing.

Blocking vs Non-blocking Assignment Infographic

electrown.com

electrown.com