Setup and hold violations occur when data signals arrive too early or too late relative to the clock edge, causing timing errors in synchronous circuits. Understanding how clock skew--variation in clock arrival times across elements--affects these violations is essential for optimizing your digital design; continue reading to explore their impact in detail.

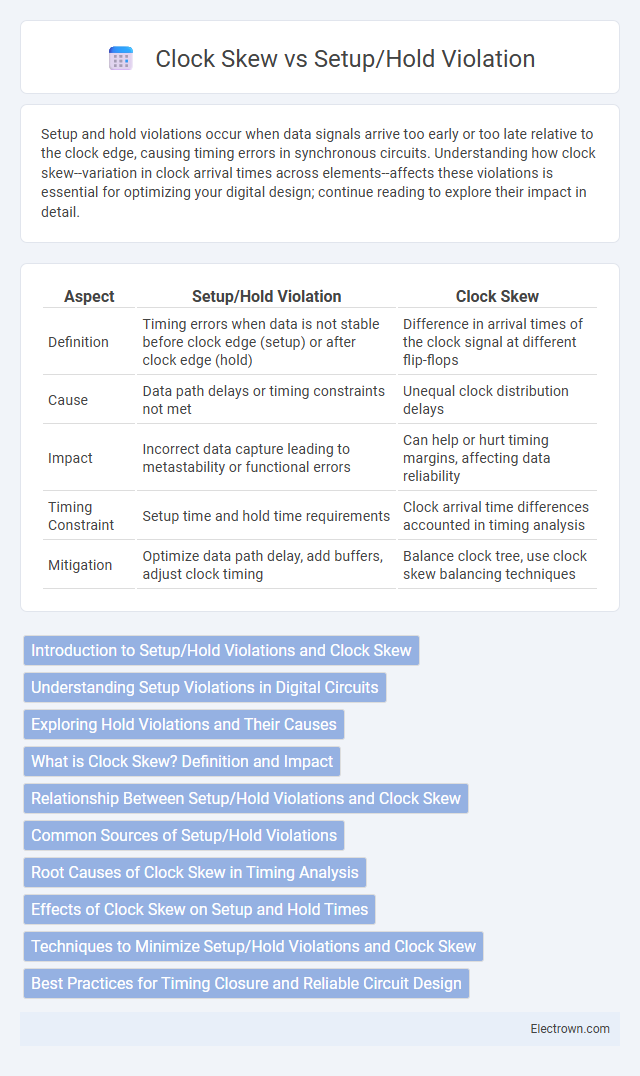

Table of Comparison

| Aspect | Setup/Hold Violation | Clock Skew |

|---|---|---|

| Definition | Timing errors when data is not stable before clock edge (setup) or after clock edge (hold) | Difference in arrival times of the clock signal at different flip-flops |

| Cause | Data path delays or timing constraints not met | Unequal clock distribution delays |

| Impact | Incorrect data capture leading to metastability or functional errors | Can help or hurt timing margins, affecting data reliability |

| Timing Constraint | Setup time and hold time requirements | Clock arrival time differences accounted in timing analysis |

| Mitigation | Optimize data path delay, add buffers, adjust clock timing | Balance clock tree, use clock skew balancing techniques |

Introduction to Setup/Hold Violations and Clock Skew

Setup and hold violations occur when data signals do not meet timing requirements relative to the clock edge, causing unreliable circuit operation. Clock skew refers to the timing difference in the arrival of the clock signal at different components, which can exacerbate these violations by altering the expected timing window. Understanding how clock skew impacts setup and hold times helps you optimize timing analysis and ensure robust digital design performance.

Understanding Setup Violations in Digital Circuits

Setup violations occur when data signals fail to stabilize before the clock's active edge, causing unreliable sampling and potential logic errors in digital circuits. Clock skew, the timing difference in clock signal arrival between flip-flops, can worsen setup violations by effectively reducing the data setup time margin. Proper timing analysis and clock distribution design are critical to minimize setup violations and ensure robust circuit performance.

Exploring Hold Violations and Their Causes

Hold violations occur when data changes too soon after the clock edge, causing setup and hold time requirements to be unmet and potentially leading to incorrect data being latched in digital circuits. Clock skew, the difference in arrival times of the clock signal at different flip-flops, is a primary cause of hold violations by effectively reducing the effective hold time margin. Understanding the interaction between clock skew and timing constraints is crucial for minimizing hold violations and ensuring reliable circuit performance.

What is Clock Skew? Definition and Impact

Clock skew refers to the timing difference between the clock signals arriving at different components or registers within a digital circuit, often caused by variations in clock path delays. This mismatch affects the accuracy of data capture, potentially leading to setup and hold violations where data fails to meet the required timing windows for valid sampling. Managing clock skew is critical in synchronous designs to ensure data integrity and prevent timing errors that can degrade overall system performance.

Relationship Between Setup/Hold Violations and Clock Skew

Setup and hold violations are timing errors that occur when data signals do not meet the required timing margins relative to the clock edge, while clock skew refers to the difference in arrival times of the clock signal at different components. Clock skew directly impacts setup and hold violations by effectively reducing or increasing the time available for data to stabilize before the clock edge, thereby influencing timing margins. Understanding your clock distribution network and minimizing clock skew helps mitigate setup and hold violations, improving overall circuit reliability and performance.

Common Sources of Setup/Hold Violations

Common sources of setup/hold violations include clock skew, insufficient data path timing, and signal integrity issues. Variations in clock arrival times cause clock skew, leading to timing mismatches between registers that result in setup or hold time failures. Your design must address these factors by optimizing clock distribution and improving data path delays to mitigate violations effectively.

Root Causes of Clock Skew in Timing Analysis

Clock skew in timing analysis primarily arises from variations in path delays due to inconsistent wire lengths and differing buffer stages within a clock distribution network. Process variations, temperature gradients, and voltage fluctuations further exacerbate skew by altering the propagation delay of clock signals. These root causes directly impact setup and hold violation margins, making accurate skew estimation essential for robust timing closure.

Effects of Clock Skew on Setup and Hold Times

Clock skew can critically impact setup and hold times by altering the effective arrival of clock signals at sequential elements, potentially causing setup violations when data arrives too late or hold violations when data arrives too early. Your timing analysis must account for positive and negative clock skew to ensure reliable circuit operation and prevent metastability. Optimizing clock distribution networks reduces skew effects, thereby securing correct data latching within specified timing windows.

Techniques to Minimize Setup/Hold Violations and Clock Skew

Techniques to minimize setup and hold violations include adjusting clock latency, balancing data path delays, and employing slack budgeting during timing analysis. Clock skew reduction is achieved by using clock tree synthesis (CTS) optimizations, inserting delay buffers, and implementing deskew circuits to synchronize clock arrival times across flip-flops. Advanced design methodologies incorporate adaptive clocking and dynamic voltage scaling to further enhance timing margin and reduce the impact of setup/hold violations and clock skew.

Best Practices for Timing Closure and Reliable Circuit Design

Setup and hold violations often result from clock skew, which misaligns data capture timing in synchronous circuits. To ensure timing closure and reliable circuit design, maintain balanced clock trees and minimize clock uncertainties using techniques like deskew buffers and insertion delays. Your design should incorporate comprehensive timing analysis tools to verify margins and prevent race conditions effectively.

Setup/hold violation vs clock skew Infographic

electrown.com

electrown.com