Edge clocking uses signal transitions on the rising or falling edge to synchronize data, offering precise timing control for high-speed applications. Level clocking relies on the clock signal's steady state to manage data flow, which can simplify design but may reduce timing accuracy; explore the rest of this article to understand which clocking method suits your needs best.

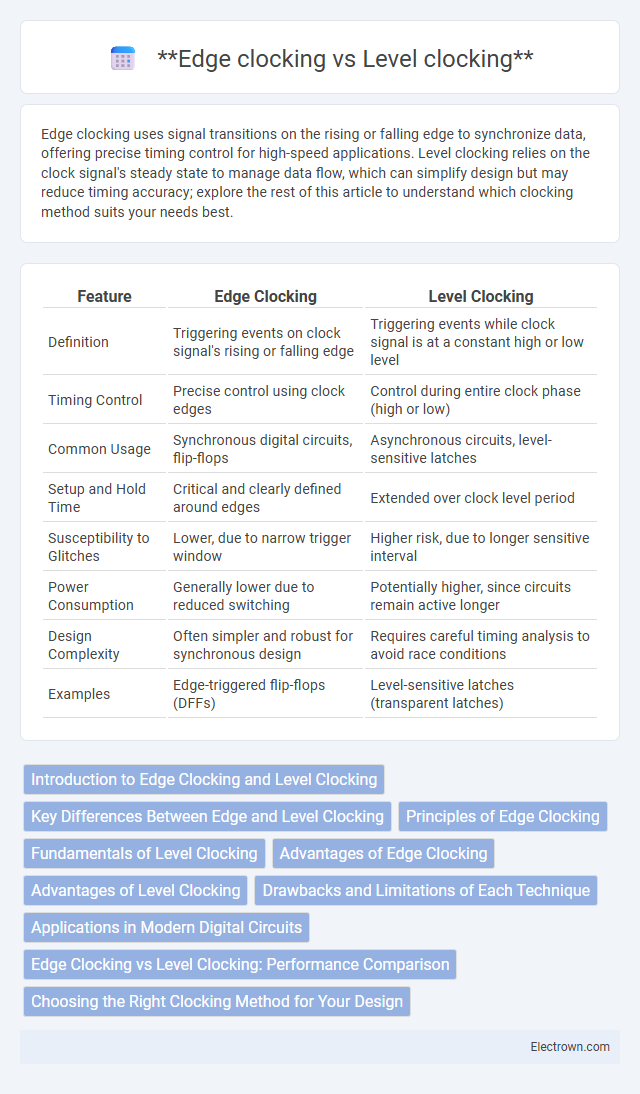

Table of Comparison

| Feature | Edge Clocking | Level Clocking |

|---|---|---|

| Definition | Triggering events on clock signal's rising or falling edge | Triggering events while clock signal is at a constant high or low level |

| Timing Control | Precise control using clock edges | Control during entire clock phase (high or low) |

| Common Usage | Synchronous digital circuits, flip-flops | Asynchronous circuits, level-sensitive latches |

| Setup and Hold Time | Critical and clearly defined around edges | Extended over clock level period |

| Susceptibility to Glitches | Lower, due to narrow trigger window | Higher risk, due to longer sensitive interval |

| Power Consumption | Generally lower due to reduced switching | Potentially higher, since circuits remain active longer |

| Design Complexity | Often simpler and robust for synchronous design | Requires careful timing analysis to avoid race conditions |

| Examples | Edge-triggered flip-flops (DFFs) | Level-sensitive latches (transparent latches) |

Introduction to Edge Clocking and Level Clocking

Edge clocking triggers circuits based on the transition of the clock signal, either on the rising or falling edge, enabling precise timing control and reduced power consumption. Level clocking activates circuits while the clock signal remains at a specific level (high or low), often resulting in simpler design but potential timing uncertainties and increased glitch susceptibility. Your choice between edge clocking and level clocking impacts timing accuracy and overall circuit performance in synchronous digital systems.

Key Differences Between Edge and Level Clocking

Edge clocking triggers data capture on the rising or falling edge of the clock signal, ensuring precise timing for sequential circuits and minimizing timing uncertainties. Level clocking maintains data activation throughout a high or low clock level, which can simplify circuit design but may increase the risk of data glitches and race conditions. Choosing between edge and level clocking depends on the specific timing requirements and complexity of the digital system design.

Principles of Edge Clocking

Edge clocking uses the transition edges of a clock signal, either rising or falling, to trigger events or data sampling, ensuring precise timing control and synchronization in digital circuits. This principle allows synchronous systems to latch data only at specific instants, minimizing timing uncertainties and race conditions common in level clocking, where signals are sampled throughout a signal's high or low level. Understanding edge clocking principles can significantly improve your circuit design's reliability by reducing glitches and improving timing accuracy.

Fundamentals of Level Clocking

Level clocking operates by maintaining a consistent voltage level during the entire active phase of a clock cycle, enabling sequential circuit elements to respond to the clock signal throughout this phase. This method contrasts with edge clocking, which triggers on the transition between voltage levels, either rising or falling edges. Understanding the fundamentals of level clocking helps you optimize timing and synchronization in digital designs where the signal stability during the active clock level is crucial for reliable data processing.

Advantages of Edge Clocking

Edge clocking offers precise timing control by triggering data transfer at specific clock signal transitions, minimizing setup and hold time violations. This method reduces power consumption as circuits activate only during clock edges, enhancing energy efficiency in high-speed designs. Edge clocking also supports higher operational frequencies by enabling faster synchronization compared to level clocking, which relies on stable clock levels.

Advantages of Level Clocking

Level clocking offers superior control over signal timing by maintaining a stable clock level throughout the operation, reducing the risk of timing errors common in edge clocking. This approach enables easier synchronization in complex digital circuits, improving reliability and predictability in sequential logic. Your designs can benefit from fewer glitches and more consistent data capture when using level clocking.

Drawbacks and Limitations of Each Technique

Edge clocking suffers from timing uncertainties and increased susceptibility to clock skew, which can cause setup and hold time violations, limiting high-frequency performance. Level clocking introduces challenges with glitch propagation and potential race conditions due to extended transparent phases, complicating timing analysis and increasing power consumption. Your system design must carefully weigh these drawbacks to optimize clocking strategy for reliable synchronous operation.

Applications in Modern Digital Circuits

Edge clocking is widely used in high-speed digital circuits such as microprocessors and synchronous memory, where precise timing control is crucial for data sampling and transfer on clock edges. Level clocking finds applications in asynchronous circuits and low-power designs, allowing data to be latched and processed during stable clock phases, reducing power consumption and noise. Modern SoCs leverage edge clocking for efficient pipeline synchronization, while level clocking supports complex state machines and handshake protocols in mixed-timing environments.

Edge Clocking vs Level Clocking: Performance Comparison

Edge clocking triggers data capture on the rising or falling edge of the clock signal, enabling faster data transfers and reduced latency in synchronous systems. Level clocking maintains data integrity by sampling during the clock's high or low level, but it often results in increased setup and hold time requirements, potentially impacting overall speed. Performance comparison reveals edge clocking is preferred in high-speed applications due to precise timing and improved throughput, while level clocking offers robustness in systems with timing uncertainties.

Choosing the Right Clocking Method for Your Design

Choosing the right clocking method between edge clocking and level clocking depends on the timing requirements and stability of your digital design. Edge clocking triggers state changes at clock signal transitions, providing precise synchronization and minimizing timing errors in high-speed circuits. Level clocking maintains a stable clock level during data transfer, which can simplify design but may introduce timing uncertainties in complex or high-frequency applications.

Edge clocking vs level clocking Infographic

electrown.com

electrown.com