Synchronous reset aligns with the clock signal, ensuring that reset actions occur only during clock transitions, which helps maintain predictable timing in your digital circuits. Discover the detailed differences and practical implications of synchronous versus asynchronous reset by reading the full article.

Table of Comparison

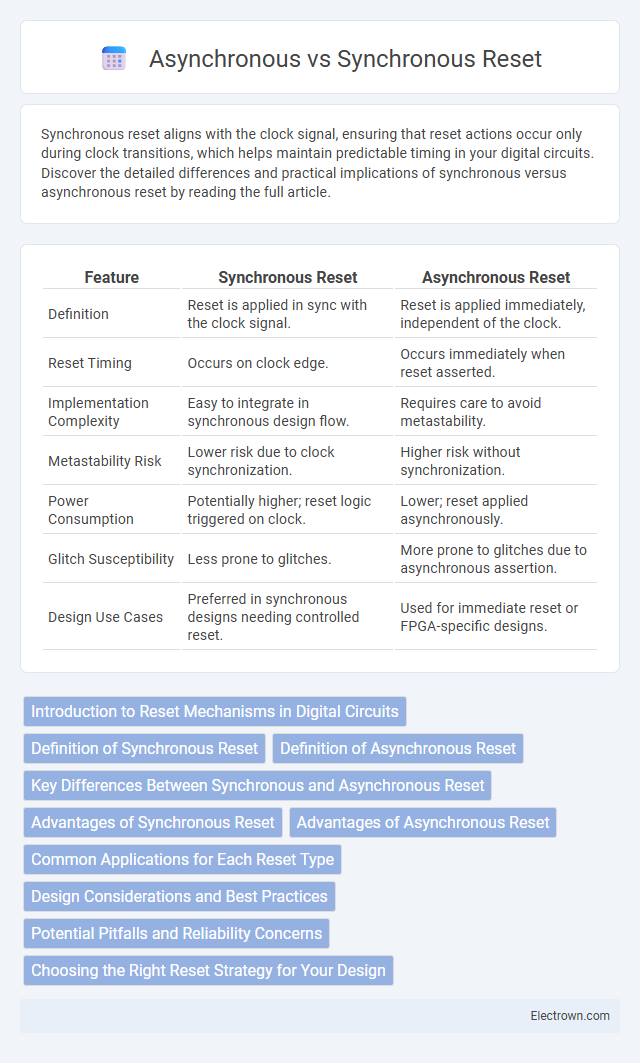

| Feature | Synchronous Reset | Asynchronous Reset |

|---|---|---|

| Definition | Reset is applied in sync with the clock signal. | Reset is applied immediately, independent of the clock. |

| Reset Timing | Occurs on clock edge. | Occurs immediately when reset asserted. |

| Implementation Complexity | Easy to integrate in synchronous design flow. | Requires care to avoid metastability. |

| Metastability Risk | Lower risk due to clock synchronization. | Higher risk without synchronization. |

| Power Consumption | Potentially higher; reset logic triggered on clock. | Lower; reset applied asynchronously. |

| Glitch Susceptibility | Less prone to glitches. | More prone to glitches due to asynchronous assertion. |

| Design Use Cases | Preferred in synchronous designs needing controlled reset. | Used for immediate reset or FPGA-specific designs. |

Introduction to Reset Mechanisms in Digital Circuits

Reset mechanisms in digital circuits serve to initialize or reinitialize flip-flops and registers to a known state, ensuring predictable circuit behavior after power-up or error conditions. Synchronous resets are clock-dependent, activating only on the clock edge and integrating smoothly into the normal timing of the system, while asynchronous resets operate independently of the clock, allowing immediate response to reset signals. Choosing between synchronous and asynchronous resets impacts circuit timing, complexity, and reliability, particularly in FPGA and ASIC designs.

Definition of Synchronous Reset

Synchronous reset is a type of reset signal in digital circuits that is synchronized with the clock signal, meaning the reset action occurs only on a specific clock edge. This ensures that the reset state is applied simultaneously with other clocked events, providing predictable timing behavior in flip-flops and registers. You benefit from easier timing analysis and reduced risk of metastability when implementing synchronous reset in your designs.

Definition of Asynchronous Reset

Asynchronous reset is a reset mechanism in digital circuits where the reset signal overrides the clock and immediately forces the system into a predefined state regardless of the clock's timing. This type of reset ensures instant response to reset commands, preventing potential timing issues during clock synchronization. It is primarily used in designs requiring immediate recovery from faults or initialization before the clock is stable.

Key Differences Between Synchronous and Asynchronous Reset

Synchronous reset occurs simultaneously with the clock signal, ensuring the reset state is applied only during clock transitions, which minimizes timing issues in digital circuits. Asynchronous reset operates independently of the clock, immediately forcing the circuit into a reset state, which can cause metastability or glitches if not properly synchronized. Understanding these key differences helps you design reliable digital systems by choosing the appropriate reset method for your application's timing requirements.

Advantages of Synchronous Reset

Synchronous reset offers precise timing control by aligning the reset signal with the clock, minimizing metastability risks and simplifying timing analysis in digital circuits. Your design benefits from reduced glitch sensitivity since the reset state changes only during clock edges, enhancing system stability and predictability. This approach is particularly advantageous in FPGA and ASIC designs where synchronized control signals optimize performance and reliability.

Advantages of Asynchronous Reset

Asynchronous reset offers faster system response by immediately resetting the circuit regardless of the clock cycle, which enhances reliability during power-up or fault conditions. It simplifies timing analysis since the reset is not dependent on clock edges, reducing the risk of metastability issues. This method improves safety in critical applications by ensuring rapid system recovery from error states without waiting for clock synchronization.

Common Applications for Each Reset Type

Synchronous reset is commonly used in digital circuits where timing control is essential, such as in flip-flops within clocked sequential logic, to ensure that resets occur in sync with the system clock. Asynchronous reset is favored in applications requiring immediate response to reset conditions, like power-on initialization and emergency stop circuits, because it can override the clock and reset the system instantly. Your choice between synchronous and asynchronous reset depends on whether precise timing alignment or rapid response is more critical for your specific electronic design.

Design Considerations and Best Practices

Synchronous reset aligns the reset signal with the clock, ensuring predictable timing but increasing complexity in the design's timing analysis, while asynchronous reset operates independently of the clock, offering faster response but risks metastability and glitches. Best practices recommend using synchronous resets in FPGA designs to avoid asynchronous issues and simplify timing closure, whereas asynchronous resets are preferred for critical reset conditions requiring immediate response. Your choice should balance reliability, timing constraints, and device technology to optimize system robustness and performance.

Potential Pitfalls and Reliability Concerns

Synchronous resets risk metastability and timing violations when reset signals do not align precisely with the clock, potentially causing unpredictable circuit behavior. Asynchronous resets can lead to reset recovery and removal time violations, resulting in partial resetting or glitches if not properly synchronized with the clock domain. Both reset methods require careful design of pulse widths, synchronization circuits, and reset de-assertion timing to ensure system reliability and stable operation.

Choosing the Right Reset Strategy for Your Design

Choosing the right reset strategy depends on the specific requirements of your digital design, such as timing constraints and power consumption. Synchronous resets integrate with the clock, offering predictable timing but potentially increasing clock load and area, while asynchronous resets provide immediate reset response independent of the clock but risk metastability and glitches if not properly synchronized. Designers must evaluate the trade-offs between deterministic reset timing and ease of integration to ensure reliable startup and robust system behavior.

Synchronous vs Asynchronous Reset Infographic

electrown.com

electrown.com