Guard rings provide effective isolation by surrounding sensitive circuit areas with a conductive barrier to prevent latch-up and reduce noise interference, while deep N-well guards enhance substrate isolation by creating a deep, doped region that blocks unwanted current paths more robustly. Understanding the differences between these techniques can help you optimize your chip design; explore the rest of the article to discover which method best suits your application.

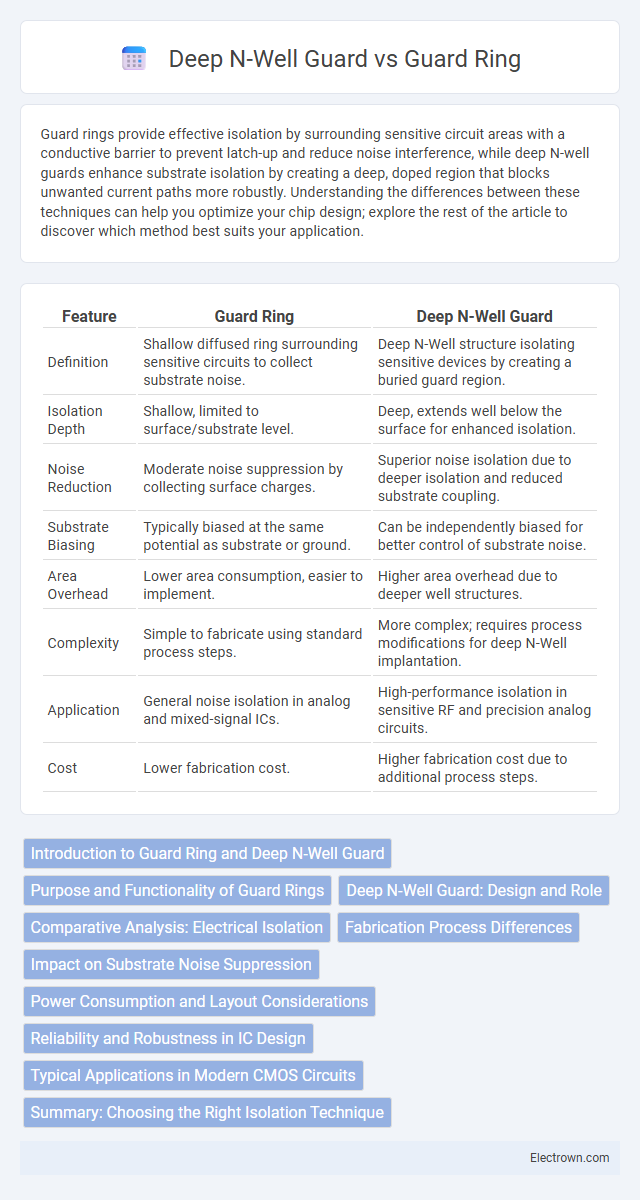

Table of Comparison

| Feature | Guard Ring | Deep N-Well Guard |

|---|---|---|

| Definition | Shallow diffused ring surrounding sensitive circuits to collect substrate noise. | Deep N-Well structure isolating sensitive devices by creating a buried guard region. |

| Isolation Depth | Shallow, limited to surface/substrate level. | Deep, extends well below the surface for enhanced isolation. |

| Noise Reduction | Moderate noise suppression by collecting surface charges. | Superior noise isolation due to deeper isolation and reduced substrate coupling. |

| Substrate Biasing | Typically biased at the same potential as substrate or ground. | Can be independently biased for better control of substrate noise. |

| Area Overhead | Lower area consumption, easier to implement. | Higher area overhead due to deeper well structures. |

| Complexity | Simple to fabricate using standard process steps. | More complex; requires process modifications for deep N-Well implantation. |

| Application | General noise isolation in analog and mixed-signal ICs. | High-performance isolation in sensitive RF and precision analog circuits. |

| Cost | Lower fabrication cost. | Higher fabrication cost due to additional process steps. |

Introduction to Guard Ring and Deep N-Well Guard

Guard Ring and Deep N-Well Guard are advanced semiconductor isolation techniques used to improve device performance and reduce leakage currents in integrated circuits. Guard Rings are typically implemented by surrounding sensitive components with heavily doped regions to create potential barriers, enhancing noise immunity and latch-up prevention. Deep N-Well Guards involve deeper substrate isolation by embedding an extended N-well region beneath the active devices, effectively suppressing substrate noise and improving transient immunity in mixed-signal and RF circuits.

Purpose and Functionality of Guard Rings

Guard rings are designed to isolate sensitive analog or mixed-signal circuits by collecting and redirecting substrate noise, thereby improving signal integrity and minimizing latch-up risks. They create a controlled potential barrier around critical components, effectively preventing charge carriers from entering the protected region. Your circuit benefits from enhanced stability and reduced interference by implementing guard rings, especially in mixed-signal IC designs.

Deep N-Well Guard: Design and Role

Deep N-Well Guard structures provide enhanced isolation by incorporating a deep n-type well beneath sensitive circuit elements, effectively reducing substrate noise and latch-up susceptibility in mixed-signal and RF IC designs. This design creates a robust electrical barrier that confines noise and prevents interference between high-voltage and low-voltage regions, improving overall device reliability and performance. Your integrated circuit benefits from improved signal integrity and protection when deep N-well guard rings are implemented in critical areas.

Comparative Analysis: Electrical Isolation

Guard Ring provides effective electrical isolation by surrounding sensitive devices with a doped semiconductor barrier, reducing leakage currents and minimizing substrate noise coupling. Deep N-Well Guard enhances isolation further by forming a deeper, high-voltage barrier within the substrate, which better isolates analog circuits from noisy digital regions and suppresses latch-up phenomena. The Deep N-Well structure offers superior isolation in mixed-signal ICs, especially where high substrate noise and complex layout constraints exist.

Fabrication Process Differences

Guard Rings are fabricated using a shallow diffusion process that forms a p-n junction around the active device area to isolate and protect against latch-up and noise interference. Deep N-Well Guards involve a deeper implantation and diffusion step, creating a buried layer beneath the surface to offer enhanced isolation by extending the guard ring effect vertically into the substrate. The Deep N-Well fabrication requires additional masking and implantation steps, increasing complexity and process time compared to the simpler Guard Ring structure.

Impact on Substrate Noise Suppression

Guard Rings provide effective substrate noise suppression by creating a low-resistance path to ground, thereby isolating sensitive circuits from noise sources. Deep N-Well Guard structures enhance noise reduction by extending isolation deep into the substrate, significantly reducing coupling through the bulk silicon. Your choice between these methods depends on noise sensitivity requirements and layout constraints, with Deep N-Well Guards offering superior performance in high-noise environments.

Power Consumption and Layout Considerations

Guard Ring structures typically consume less power compared to Deep N-Well Guard due to their simpler implantation and reduced substrate biasing requirements. Layout considerations for Guard Rings emphasize minimal area overhead and ease of integration in dense designs, whereas Deep N-Well Guards demand larger silicon real estate and careful isolation to prevent noise coupling. Your choice between these techniques should balance power efficiency with layout constraints, especially in mixed-signal or high-voltage applications.

Reliability and Robustness in IC Design

Guard rings provide enhanced isolation by surrounding sensitive circuit elements with a grounded diffusion layer, improving latch-up immunity and reducing substrate noise in IC designs. Deep N-Well Guard structures offer superior protection by creating a thick, high-resistivity barrier that effectively isolates NMOS devices from substrate noise and latch-up events, increasing overall device robustness. Reliability in IC design significantly improves with Deep N-Well Guards due to their enhanced electrostatic discharge (ESD) resilience and minimized parasitic interactions compared to traditional guard rings.

Typical Applications in Modern CMOS Circuits

Guard Rings are commonly employed in analog and RF CMOS circuits to isolate sensitive transistor regions from substrate noise, improving latch-up immunity and reducing substrate coupling. Deep N-Well Guards find typical applications in mixed-signal and high-voltage CMOS processes where enhanced isolation between digital and analog blocks is critical for minimizing noise interference. Both techniques contribute significantly to the reliability and performance of integrated circuits in automotive, communication, and sensor interface designs.

Summary: Choosing the Right Isolation Technique

Guard Ring provides effective surface isolation by surrounding sensitive components with a doped region, minimizing leakage currents and latch-up risk in CMOS circuits. Deep N-Well Guard offers enhanced isolation by extending deeper into the substrate, effectively isolating noisy digital blocks from sensitive analog circuitry to reduce substrate noise coupling. Selecting between these techniques depends on the circuit complexity, noise sensitivity, and process constraints, with Deep N-Well Guards preferred for mixed-signal ICs requiring superior noise isolation.

Guard Ring vs Deep N-Well Guard Infographic

electrown.com

electrown.com