Phase-Locked Loop (PLL) and Delay-Locked Loop (DLL) are crucial components in timing and synchronization for electronic systems, with PLLs primarily locking output phase to an input signal's phase and DLLs aligning signal delays to reference signals. Understanding the differences between PLL and DLL can enhance Your design choices and optimize system performance; explore the rest of the article to dive deeper into their mechanisms and applications.

Table of Comparison

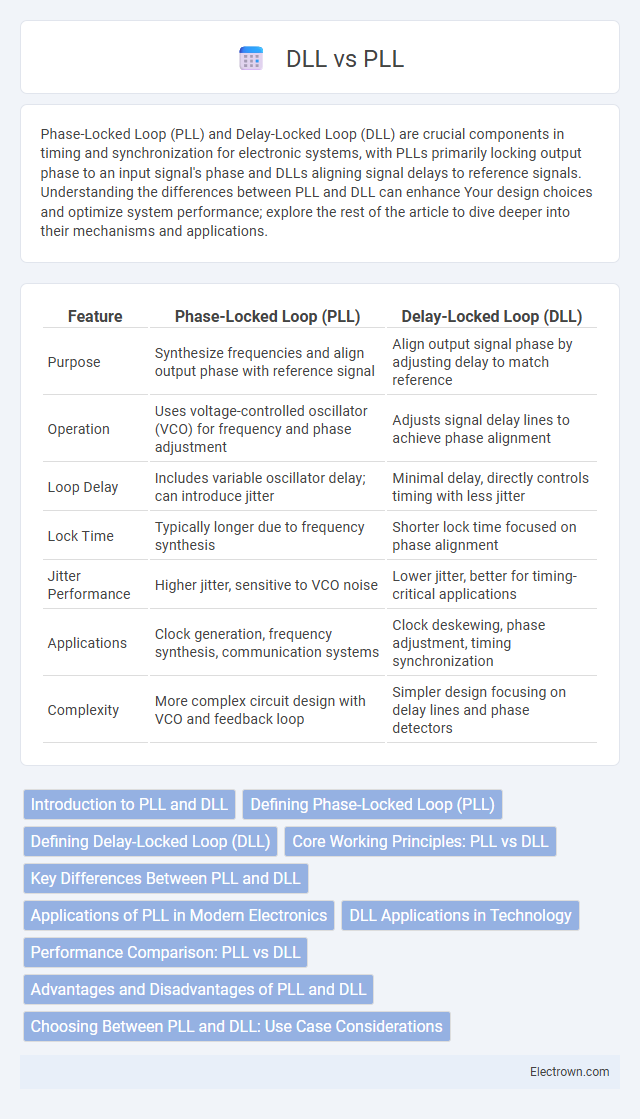

| Feature | Phase-Locked Loop (PLL) | Delay-Locked Loop (DLL) |

|---|---|---|

| Purpose | Synthesize frequencies and align output phase with reference signal | Align output signal phase by adjusting delay to match reference |

| Operation | Uses voltage-controlled oscillator (VCO) for frequency and phase adjustment | Adjusts signal delay lines to achieve phase alignment |

| Loop Delay | Includes variable oscillator delay; can introduce jitter | Minimal delay, directly controls timing with less jitter |

| Lock Time | Typically longer due to frequency synthesis | Shorter lock time focused on phase alignment |

| Jitter Performance | Higher jitter, sensitive to VCO noise | Lower jitter, better for timing-critical applications |

| Applications | Clock generation, frequency synthesis, communication systems | Clock deskewing, phase adjustment, timing synchronization |

| Complexity | More complex circuit design with VCO and feedback loop | Simpler design focusing on delay lines and phase detectors |

Introduction to PLL and DLL

A Phase-Locked Loop (PLL) is an electronic control system that synchronizes an output oscillator signal with a reference signal in both frequency and phase, widely used in communication systems and signal processing. A Delay-Locked Loop (DLL) primarily adjusts the delay of its control signal to align clock phases, enhancing timing accuracy and reducing jitter in digital circuits. Both PLLs and DLLs are essential for clock recovery and timing synchronization, but their operational mechanisms differentiate their applications in high-speed electronics.

Defining Phase-Locked Loop (PLL)

Phase-Locked Loop (PLL) is an electronic control system that synchronizes an output signal's phase and frequency with a reference signal, ensuring precise timing in communication and signal processing applications. Unlike Delay-Locked Loop (DLL), which adjusts only the phase delay, PLL continuously corrects both phase and frequency, making it ideal for stable frequency generation and clock synchronization. Your electronic design can benefit from PLL's ability to maintain signal coherence and reduce jitter in complex circuits.

Defining Delay-Locked Loop (DLL)

A Delay-Locked Loop (DLL) is a clock synchronization circuit that aligns the output clock phase with the input clock by adjusting delay elements, eliminating phase errors without frequency changes. Unlike Phase-Locked Loops (PLLs), DLLs use a variable delay line instead of a voltage-controlled oscillator, resulting in reduced jitter and improved stability. DLLs are widely used in clock data recovery and memory interfaces where precise timing alignment is critical.

Core Working Principles: PLL vs DLL

A Phase-Locked Loop (PLL) operates by continuously comparing the phase of an input signal with that of a controlled oscillator, adjusting the oscillator to maintain a constant phase difference, which ensures frequency synchronization. In contrast, a Delay-Locked Loop (DLL) focuses on aligning the timing of its output clock edges with an input clock by adjusting delay elements to match phase without generating a new frequency. Your choice between PLL and DLL depends on whether frequency synthesis or precise timing alignment is the primary requirement in your system design.

Key Differences Between PLL and DLL

Phase-Locked Loops (PLLs) and Delay-Locked Loops (DLLs) both synchronize signal timing but differ fundamentally in operation: PLLs adjust the phase and frequency of an oscillator to match a reference signal, while DLLs only delay the input signal to align phases without frequency changes. PLLs generate an output with a variable frequency, making them suitable for clock generation and frequency synthesis, whereas DLLs maintain the same output frequency as the input, ensuring precise phase alignment ideal for clock deskewing and timing adjustments. Your choice between PLL and DLL depends on whether frequency modulation or pure phase alignment is critical in your application.

Applications of PLL in Modern Electronics

Phase-Locked Loops (PLLs) are extensively used in modern electronics for signal synchronization, frequency synthesis, and clock generation in communication systems, microprocessors, and consumer devices. Their ability to lock the output signal phase to a reference makes them essential in RF transmitters, receivers, and digital circuits requiring precise timing. You will find PLLs crucial for maintaining stability and accuracy in applications like radio transmitters, data converters, and clock recovery circuits.

DLL Applications in Technology

Delay-Locked Loops (DLLs) are widely used in high-speed digital systems such as memory interfaces, clock distribution networks, and phase alignment circuits due to their ability to provide precise timing adjustments without frequency multiplication. Unlike Phase-Locked Loops (PLLs), DLLs effectively minimize jitter and delay variations in applications like DDR SDRAM timing, improving overall system reliability and data integrity. Their implementation in FPGA clock management and Serializer/Deserializer (SerDes) circuits enhances signal synchronization, making DLLs critical for modern communication and computing devices.

Performance Comparison: PLL vs DLL

Phase-Locked Loops (PLL) offer superior frequency synthesis and jitter filtering capabilities, making them ideal for applications requiring precise clock generation and high-frequency stability. Delay-Locked Loops (DLL) provide better phase alignment and faster lock times, enhancing performance in low-jitter clock distribution and timing correction scenarios. Overall, PLLs deliver higher frequency accuracy and filtering performance, while DLLs excel in minimizing phase errors and reducing latency in digital timing systems.

Advantages and Disadvantages of PLL and DLL

Phase-Locked Loops (PLL) offer advantages such as precise frequency synthesis, low jitter, and effective noise filtering, making them ideal for clock generation and synchronization in communication systems. Delay-Locked Loops (DLL) excel in faster lock times and reduced phase noise, benefiting timing adjustment and clock alignment applications, but can suffer from limited frequency range and sensitivity to process variations. Your choice between PLL and DLL depends on specific needs for stability, speed, and application context in electronic design.

Choosing Between PLL and DLL: Use Case Considerations

Phase-Locked Loop (PLL) is preferred for applications needing frequency synthesis and clock generation with continuous phase tracking, while Delay-Locked Loop (DLL) suits precise timing alignment and clock deskewing without frequency modulation. PLLs excel in communication systems requiring stable frequency locks and jitter reduction, whereas DLLs are ideal in high-speed digital circuits for minimizing clock skew and ensuring signal synchronization. Choosing between PLL and DLL depends on system requirements for frequency stability versus phase accuracy and the complexity of implementation.

PLL vs DLL Infographic

electrown.com

electrown.com