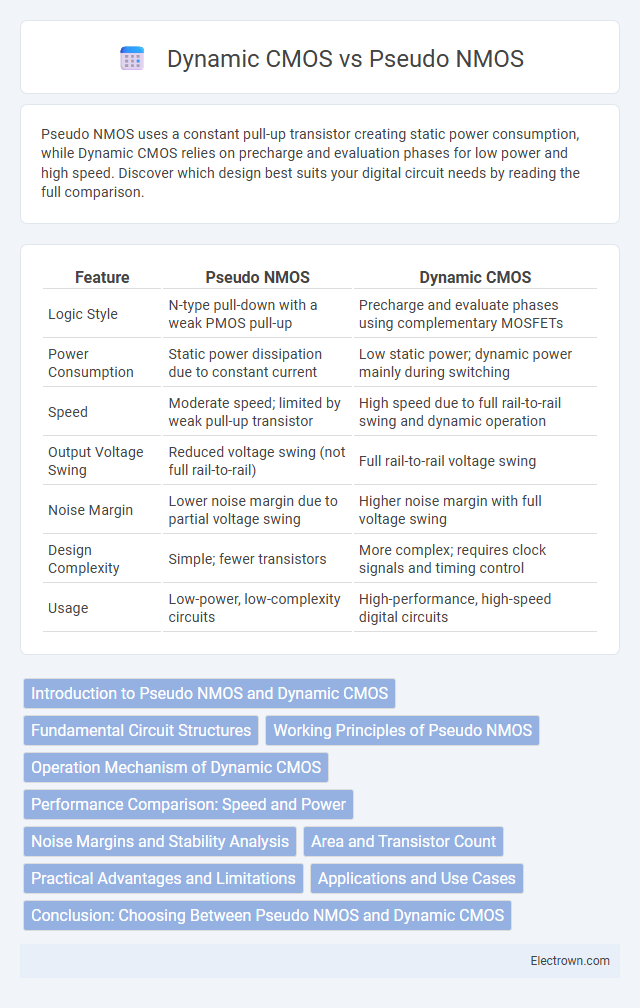

Pseudo NMOS uses a constant pull-up transistor creating static power consumption, while Dynamic CMOS relies on precharge and evaluation phases for low power and high speed. Discover which design best suits your digital circuit needs by reading the full comparison.

Table of Comparison

| Feature | Pseudo NMOS | Dynamic CMOS |

|---|---|---|

| Logic Style | N-type pull-down with a weak PMOS pull-up | Precharge and evaluate phases using complementary MOSFETs |

| Power Consumption | Static power dissipation due to constant current | Low static power; dynamic power mainly during switching |

| Speed | Moderate speed; limited by weak pull-up transistor | High speed due to full rail-to-rail swing and dynamic operation |

| Output Voltage Swing | Reduced voltage swing (not full rail-to-rail) | Full rail-to-rail voltage swing |

| Noise Margin | Lower noise margin due to partial voltage swing | Higher noise margin with full voltage swing |

| Design Complexity | Simple; fewer transistors | More complex; requires clock signals and timing control |

| Usage | Low-power, low-complexity circuits | High-performance, high-speed digital circuits |

Introduction to Pseudo NMOS and Dynamic CMOS

Pseudo NMOS logic uses a permanent pull-up transistor, typically a weak PMOS, combined with NMOS transistors to implement digital logic with reduced transistor count and faster switching. Dynamic CMOS logic employs a clocked precharge and evaluation phase, utilizing both PMOS and NMOS transistors to achieve high speed and low power consumption by exploiting charge storage on internal nodes. Your choice between Pseudo NMOS and Dynamic CMOS depends on trade-offs in static power dissipation, noise margin, and circuit complexity.

Fundamental Circuit Structures

Pseudo NMOS utilizes a simple structure with a PMOS transistor wired as a weak load and an NMOS transistor for pull-down, resulting in continuous static power consumption. Dynamic CMOS features a more complex configuration with complementary transistors and a clocked precharge phase, enhancing speed and reducing static power draw. Your choice between these fundamental circuit structures affects both power efficiency and switching performance in digital logic designs.

Working Principles of Pseudo NMOS

Pseudo NMOS logic operates by using a weak always-on NMOS transistor as a pull-down device and a PMOS transistor as a load, eliminating the need for a full complementary pair. This design allows for quicker switching speeds since the NMOS transistor actively pulls the output low, but it consumes static power due to the direct current path from VDD to ground when the output is low. Your circuit benefits from simpler layout and higher speed at the expense of increased power dissipation compared to dynamic CMOS, which uses precharge and evaluation phases to reduce static power consumption.

Operation Mechanism of Dynamic CMOS

Dynamic CMOS operates by precharging the output node to a high voltage during the clock's precharge phase, then conditionally discharging it during evaluation based on the inputs, leveraging a combination of PMOS and NMOS transistors to achieve faster switching and reduced static power consumption. This clocked operation contrasts with Pseudo NMOS, which uses a weak PMOS load transistor continuously pulling the output high, causing static power dissipation. Your choice of logic style impacts speed, power efficiency, and noise margins, with Dynamic CMOS offering superior performance for high-speed digital circuits.

Performance Comparison: Speed and Power

Pseudo NMOS circuits exhibit faster switching speeds than dynamic CMOS due to the constant pull-down network, which reduces delay but incurs higher static power consumption from continuous current flow. Dynamic CMOS designs optimize power efficiency by precharging nodes and evaluating only when necessary, resulting in significantly lower static power dissipation despite slightly slower operation speeds. Speed-critical applications favor pseudo NMOS for its rapid transitions, while dynamic CMOS is preferred in low-power environments to minimize leakage and dynamic power.

Noise Margins and Stability Analysis

Pseudo NMOS logic exhibits reduced noise margins compared to Dynamic CMOS because its pull-up transistor is always partially on, leading to higher static current and susceptibility to noise. Dynamic CMOS circuits offer improved stability through precharge and evaluation phases, which help maintain charge on nodes, providing higher noise immunity and better noise margin characteristics. Stability analysis reveals Dynamic CMOS benefits from charge retention techniques that reduce vulnerability to noise and leakage currents, unlike Pseudo NMOS that relies on continuous current flow causing potential variability in logic levels.

Area and Transistor Count

Pseudo NMOS logic typically requires fewer transistors than dynamic CMOS, leading to a smaller overall area due to its use of a single pull-up transistor and NMOS pull-down network. Dynamic CMOS circuits often need more transistors, including clocked precharge and evaluation transistors, which increase the layout size and complexity. Your choice between them will impact chip area efficiency, where Pseudo NMOS offers compactness but at the cost of static power consumption, unlike the larger but power-efficient dynamic CMOS implementation.

Practical Advantages and Limitations

Pseudo NMOS logic offers advantages like reduced transistor count and simpler fabrication, leading to faster switching speeds and lower area consumption. However, its static power dissipation due to the always-on PMOS transistor limits energy efficiency and scalability. Dynamic CMOS circuits provide better power efficiency by precharging nodes and eliminating steady-state current, but they suffer from increased design complexity, charge sharing, and susceptibility to noise, making reliable operation more challenging.

Applications and Use Cases

Pseudo NMOS logic excels in high-speed applications like clock generation and simple digital circuits due to its reduced transistor count and faster switching. Dynamic CMOS logic is preferred in complex, high-performance microprocessors and memory circuits where low power consumption and noise immunity are critical. Your design choices depend heavily on the trade-offs between power efficiency, speed, and circuit complexity in these specific applications.

Conclusion: Choosing Between Pseudo NMOS and Dynamic CMOS

Choosing between Pseudo NMOS and Dynamic CMOS depends on the desired power efficiency and speed of your circuit design. Pseudo NMOS circuits offer simpler implementation and faster switching but consume static power due to constant current flow. Dynamic CMOS provides lower power consumption and higher noise margins but requires careful clocking and precharge control to avoid logic errors.

Pseudo NMOS vs Dynamic CMOS Infographic

electrown.com

electrown.com