Non-overlapping clock signals prevent timing errors by ensuring distinct high phases for each clock signal without overlap, which is crucial in synchronous circuits to avoid race conditions. Understanding the differences between non-overlapping and overlapping clock signals can optimize your circuit design efficiency; read on to explore the detailed advantages and applications of each clock type.

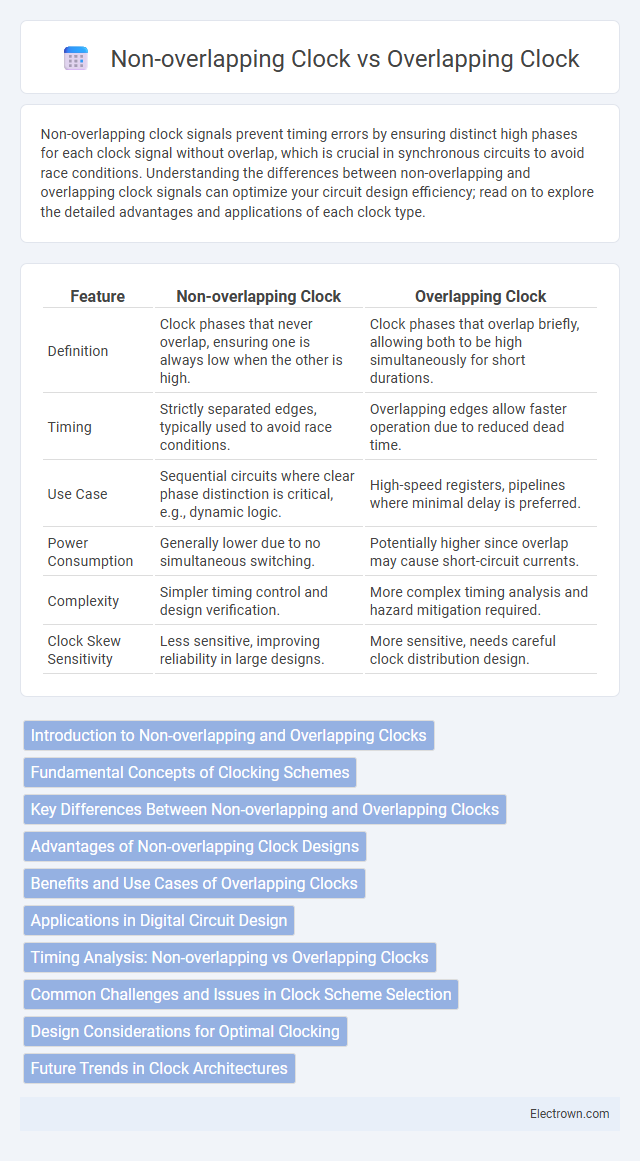

Table of Comparison

| Feature | Non-overlapping Clock | Overlapping Clock |

|---|---|---|

| Definition | Clock phases that never overlap, ensuring one is always low when the other is high. | Clock phases that overlap briefly, allowing both to be high simultaneously for short durations. |

| Timing | Strictly separated edges, typically used to avoid race conditions. | Overlapping edges allow faster operation due to reduced dead time. |

| Use Case | Sequential circuits where clear phase distinction is critical, e.g., dynamic logic. | High-speed registers, pipelines where minimal delay is preferred. |

| Power Consumption | Generally lower due to no simultaneous switching. | Potentially higher since overlap may cause short-circuit currents. |

| Complexity | Simpler timing control and design verification. | More complex timing analysis and hazard mitigation required. |

| Clock Skew Sensitivity | Less sensitive, improving reliability in large designs. | More sensitive, needs careful clock distribution design. |

Introduction to Non-overlapping and Overlapping Clocks

Non-overlapping clocks are timing signals designed to prevent simultaneous high states on related clock lines, ensuring that no two clock phases overlap to avoid glitches in digital circuits. Overlapping clocks, by contrast, allow brief periods where multiple clock phases are high simultaneously, enabling faster transitions but requiring careful design to prevent timing errors. Your choice between non-overlapping and overlapping clocks impacts circuit complexity, power consumption, and timing reliability in synchronous systems.

Fundamental Concepts of Clocking Schemes

Non-overlapping clock schemes use two or more clock phases that do not overlap to prevent simultaneous switching, reducing short-circuit current and ensuring proper sequencing in digital circuits. Overlapping clock schemes allow clock phases to overlap, enabling faster data transfer and improved timing efficiency but require careful management of race conditions and hazards. Your choice between these clocking schemes impacts power consumption, timing reliability, and overall circuit performance.

Key Differences Between Non-overlapping and Overlapping Clocks

Non-overlapping clocks have distinct, non-simultaneous activation phases ensuring no overlap between clock signals, reducing short-circuit risks and timing hazards in sequential circuits. Overlapping clocks, on the other hand, allow certain simultaneous transitions in clock phases to optimize speed and resource utilization but require complex timing analysis to avoid data corruption. Your choice between these clocking schemes depends on the trade-off between circuit simplicity and performance requirements.

Advantages of Non-overlapping Clock Designs

Non-overlapping clock designs offer enhanced signal integrity by preventing simultaneous activation of clock phases, which reduces short-circuit currents and minimizes power consumption. They improve timing reliability in sequential circuits by eliminating race conditions and glitches that can occur in overlapping clock schemes. This design approach simplifies timing analysis and enhances overall system stability in clocked digital systems.

Benefits and Use Cases of Overlapping Clocks

Overlapping clocks enable higher operational speeds by allowing timing windows to intersect, reducing idle periods and enhancing throughput in digital circuits. Your design benefits from improved clock utilization and faster data processing, especially in high-performance applications like pipelined processors and synchronous memory systems. These clocks are ideal when tight timing constraints require efficient handoff between sequential stages without introducing race conditions.

Applications in Digital Circuit Design

Non-overlapping clocks are crucial in preventing race conditions and glitches in sequential digital circuits such as shift registers and dynamic flip-flops, ensuring data integrity by creating distinct timing windows. Overlapping clocks, on the other hand, enable faster data transfer in pipelined architectures and high-speed sampling circuits by allowing the clock phases to overlap, thereby reducing latency. Your choice between these clocking schemes impacts the performance and reliability of digital systems in applications like microprocessors and memory arrays.

Timing Analysis: Non-overlapping vs Overlapping Clocks

Timing analysis of non-overlapping clocks ensures that two clock signals never assert simultaneously, minimizing the risk of race conditions and data corruption in sequential circuits. Overlapping clocks, by allowing clocks to be asserted concurrently, can improve throughput but require careful timing verification to prevent setup and hold time violations. Your timing analysis strategy must account for these differences to ensure reliable operation in clocked digital systems.

Common Challenges and Issues in Clock Scheme Selection

Non-overlapping clock schemes often face challenges in timing complexity and increased design area due to strict non-overlap requirements, which can lead to inefficient power consumption and gating difficulties. Overlapping clocks, while simplifying timing and reducing latency, introduce risks of race conditions and hold time violations, complicating synchronization in sequential circuits. Selecting between these schemes requires balancing trade-offs in timing reliability, power efficiency, and area overhead to fit specific application constraints.

Design Considerations for Optimal Clocking

Design considerations for optimal clocking focus on minimizing timing hazards and ensuring reliable data transfer between sequential circuits. Non-overlapping clocks guarantee a dead time between clock phases, reducing clock skew and preventing short-circuit currents in dynamic logic circuits. Overlapping clocks can improve throughput by allowing data to propagate with reduced latency but demand precise phase alignment and careful management of timing margins to avoid race conditions.

Future Trends in Clock Architectures

Non-overlapping clock architectures minimize timing errors by ensuring distinct, non-overlapping clock phases, but emerging trends favor overlapping clock designs for higher integration and reduced latency in advanced CPUs and AI accelerators. Innovations in synchronized multi-phase clocks leverage overlapping techniques to optimize power efficiency and frequency scaling, crucial for future high-performance computing systems. Your design considerations should weigh these architecture trends as semiconductor technology advances toward smaller nodes and more complex timing requirements.

Non-overlapping Clock vs Overlapping Clock Infographic

electrown.com

electrown.com