Synchronous FIFO operates with a single clock signal, ensuring data is transferred smoothly within the same timing domain, while Asynchronous FIFO manages data transfer between different clock domains, using separate read and write clocks to prevent timing issues. Explore the rest of the article to understand which FIFO type best suits your design needs.

Table of Comparison

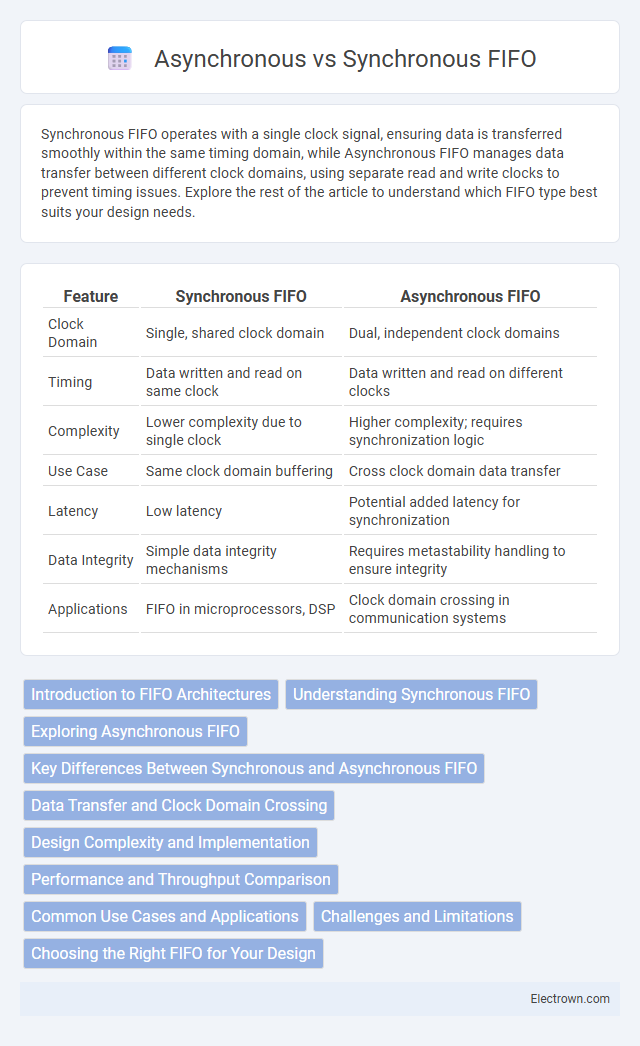

| Feature | Synchronous FIFO | Asynchronous FIFO |

|---|---|---|

| Clock Domain | Single, shared clock domain | Dual, independent clock domains |

| Timing | Data written and read on same clock | Data written and read on different clocks |

| Complexity | Lower complexity due to single clock | Higher complexity; requires synchronization logic |

| Use Case | Same clock domain buffering | Cross clock domain data transfer |

| Latency | Low latency | Potential added latency for synchronization |

| Data Integrity | Simple data integrity mechanisms | Requires metastability handling to ensure integrity |

| Applications | FIFO in microprocessors, DSP | Clock domain crossing in communication systems |

Introduction to FIFO Architectures

Synchronous FIFO architectures operate with a single clock domain, ensuring data is written and read in lockstep, which simplifies timing analysis and reduces latency. Asynchronous FIFO designs handle data transfer between different clock domains, using dual-port memory and gray-coded pointers to prevent metastability and ensure data integrity. Understanding the distinction helps you choose the appropriate FIFO architecture based on your system's timing and synchronization requirements.

Understanding Synchronous FIFO

Synchronous FIFO operates with a single clock domain, ensuring data is stored and retrieved based on the same clock signal. This design minimizes timing issues and simplifies control logic, making it ideal for applications requiring predictable data flow and low-latency communication. Your system benefits from consistent data throughput when using synchronous FIFO due to its tightly coordinated read and write operations.

Exploring Asynchronous FIFO

Asynchronous FIFO buffers operate with independent read and write clocks, enabling data transfer between different clock domains without requiring synchronization. This design reduces timing-related issues such as metastability, ensuring reliable communication in complex digital systems. Your system benefits from seamless data flow and improved performance when integrating asynchronous FIFOs in mixed clock environments.

Key Differences Between Synchronous and Asynchronous FIFO

Synchronous FIFO operates with a single clock domain, allowing data to be written and read using the same clock signal, which simplifies timing but limits flexibility. Asynchronous FIFO supports different clock domains for writing and reading, enabling data transfer between systems operating at different clock rates while requiring complex synchronization circuits to prevent metastability. The key difference lies in clock domain usage, where synchronous FIFO excels in environments with uniform timing, and asynchronous FIFO is essential for bridging asynchronous systems.

Data Transfer and Clock Domain Crossing

Synchronous FIFO uses a single clock domain, ensuring straightforward data transfer with minimal latency since both read and write operations occur under the same clock signal. Asynchronous FIFO enables data transfer across different clock domains, employing dual-clock pointers and Gray code to manage metastability and ensure reliable data synchronization. Clock domain crossing in asynchronous FIFOs is critical for preventing data corruption and requires careful design to maintain data integrity between different timing domains.

Design Complexity and Implementation

Synchronous FIFO design is simpler due to a single clock domain, allowing easier timing analysis and straightforward implementation with fewer synchronization circuits. Asynchronous FIFO involves multiple clock domains, increasing design complexity by requiring careful management of clock domain crossing and metastability mitigation through techniques like Gray code pointers and dual-port memory. Your choice depends on the system requirements, as asynchronous FIFOs provide flexibility at the cost of more intricate design and verification challenges.

Performance and Throughput Comparison

Synchronous FIFO operates with a single clock domain, enabling faster data transfer rates and lower latency, which enhances overall performance in applications where timing uniformity is critical. Asynchronous FIFO manages data across different clock domains, introducing additional synchronization stages that can slightly reduce throughput but provide robust clock domain crossing and flexibility. Your choice between synchronous and asynchronous FIFO directly impacts system throughput, with synchronous FIFO typically offering higher performance in homogeneous clock environments.

Common Use Cases and Applications

Synchronous FIFOs are typically used in applications requiring data transfer between components operating under the same clock domain, such as in pipelined processor architectures and digital signal processing systems. Asynchronous FIFOs are essential in systems involving crossing between different clock domains, commonly found in communication interfaces, data buffering between peripherals, and FPGA designs interfacing with external hardware. Both FIFO types are crucial for managing data flow, avoiding data loss, and maintaining system reliability in embedded systems, high-speed networking, and real-time data streaming applications.

Challenges and Limitations

Synchronous FIFO faces challenges in clock domain crossing, making it unsuitable for systems with multiple clock sources due to timing and synchronization issues. Asynchronous FIFO overcomes these challenges but introduces complexity in pointer management and metastability, which can limit data throughput and increase latency if not properly designed. Your system's choice between synchronous and asynchronous FIFO must consider these trade-offs to optimize performance and reliability.

Choosing the Right FIFO for Your Design

Selecting the right FIFO for your design hinges on the clock domains involved; synchronous FIFO is ideal when data producer and consumer share the same clock, ensuring minimal latency and simpler control logic. Asynchronous FIFO excels in designs where different clock domains exist, providing reliable data transfer across clock boundaries through dual-port memory and handshake control. Understanding these distinctions helps you optimize performance and data integrity in your digital system.

Synchronous vs Asynchronous FIFO Infographic

electrown.com

electrown.com