Static latches maintain their stored state as long as power is supplied, relying on feedback loops for data retention, while dynamic latches store data temporarily using capacitors, requiring periodic refreshes to prevent data loss. Understanding the differences between static and dynamic latches can help you optimize your circuit design; explore the rest of the article to learn more about their applications and trade-offs.

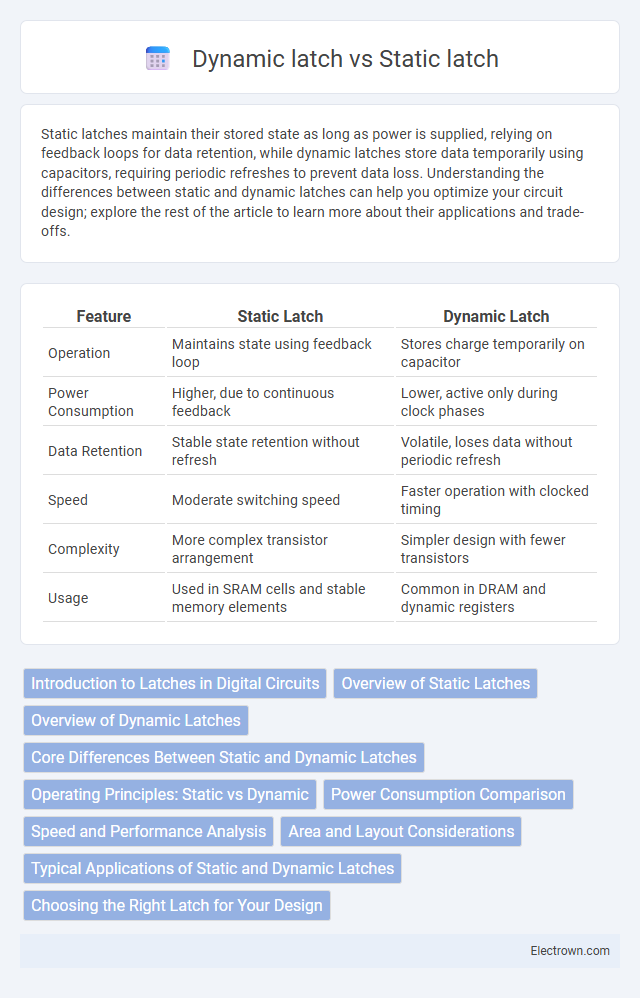

Table of Comparison

| Feature | Static Latch | Dynamic Latch |

|---|---|---|

| Operation | Maintains state using feedback loop | Stores charge temporarily on capacitor |

| Power Consumption | Higher, due to continuous feedback | Lower, active only during clock phases |

| Data Retention | Stable state retention without refresh | Volatile, loses data without periodic refresh |

| Speed | Moderate switching speed | Faster operation with clocked timing |

| Complexity | More complex transistor arrangement | Simpler design with fewer transistors |

| Usage | Used in SRAM cells and stable memory elements | Common in DRAM and dynamic registers |

Introduction to Latches in Digital Circuits

Static latches store data using feedback loops formed by cross-coupled inverters, maintaining state as long as power is supplied without requiring clock signals. Dynamic latches rely on temporary charge storage on capacitive nodes, requiring periodic clocking to refresh data and are susceptible to charge leakage over time. Both types play critical roles in digital circuits for temporary data storage, with static latches favored for robustness and dynamic latches for speed and area efficiency.

Overview of Static Latches

Static latches utilize feedback mechanisms to maintain a stable logic state, ensuring data retention without the need for periodic refresh signals. They consist of cross-coupled inverters that hold the stored value as long as power is supplied, making them reliable for long-term data storage. These latches offer lower complexity and greater noise immunity compared to dynamic latches, which rely on charge storage and require refresh cycles.

Overview of Dynamic Latches

Dynamic latches utilize transient storage of charge on a capacitor to hold data, enabling faster operation and lower power consumption compared to static latches, which rely on bistable feedback circuits for data retention. Your design can benefit from dynamic latches in high-speed applications where minimizing transistor count and area is critical, although they require careful timing control to prevent data loss due to charge leakage. These characteristics make dynamic latches ideal for use in clocked digital systems such as pipeline registers and high-performance microprocessors.

Core Differences Between Static and Dynamic Latches

Static latches use feedback loops to maintain their state indefinitely, ensuring data stability without refreshing, while dynamic latches rely on stored charge in capacitors that require periodic refreshing to prevent data loss. The core difference lies in power consumption and data retention: static latches consume more power due to continuous feedback, whereas dynamic latches are more power-efficient but vulnerable to charge leakage, limiting their hold time. Furthermore, static latches offer better noise immunity and robustness, making them suitable for stable memory elements, whereas dynamic latches are preferred in high-speed, low-power applications where periodic refresh is manageable.

Operating Principles: Static vs Dynamic

Static latches store data using feedback loops made of cross-coupled inverters, maintaining the stored value as long as power is supplied without needing a clock signal. Dynamic latches rely on capacitive storage and the clock signal's phase to hold data temporarily, making them more susceptible to charge leakage and requiring periodic refreshing. Your choice between static and dynamic latches impacts data stability, power consumption, and speed in digital circuits.

Power Consumption Comparison

Static latches consume less power during idle states because they maintain their output without continuous clocking, relying on feedback loops in their bistable circuit structure. Dynamic latches, on the other hand, exhibit higher power consumption due to their reliance on clocked capacitive storage, which causes charging and discharging activities in every clock cycle. As a result, static latches are preferred in low-power applications, while dynamic latches may lead to increased dynamic power dissipation in high-frequency circuits.

Speed and Performance Analysis

Static latches offer lower power consumption and more reliable data retention by using feedback loops, but they typically have slower speed due to increased transistor count and parasitic capacitances. Dynamic latches achieve higher speed and improved performance by storing charge on capacitive nodes, allowing faster transitions and reduced propagation delay, though they require periodic refreshing to maintain data integrity. In high-frequency applications, dynamic latches are preferred for speed-critical paths, while static latches excel in power-sensitive and noise-resilient environments.

Area and Layout Considerations

Static latches typically occupy larger silicon area due to their use of cross-coupled inverters and feedback transistors, which require more layout space. Dynamic latches benefit from reduced transistor counts and simplified layouts, resulting in smaller area footprints but demand careful charge retention management. Your design choice can influence overall chip density and routing complexity depending on these area and layout trade-offs.

Typical Applications of Static and Dynamic Latches

Static latches are primarily used in applications requiring low power consumption and data stability, such as memory elements in SRAM and state-holding circuits in microcontrollers. Dynamic latches are favored in high-speed and clocked circuits like DRAM sense amplifiers and pipeline stages in CPUs due to their faster operation and smaller area. Both types are essential in digital design, with static latches offering robustness in asynchronous systems and dynamic latches enabling higher performance in synchronous, timing-critical applications.

Choosing the Right Latch for Your Design

Selecting between static and dynamic latches depends on factors like power consumption, speed, and area constraints. Static latches offer robustness and data stability due to their feedback mechanisms, making them ideal for low-power, noise-sensitive applications. Dynamic latches provide faster operation and reduced transistor count, suitable for high-speed designs where clock timing and refresh are carefully managed.

Static latch vs dynamic latch Infographic

electrown.com

electrown.com