Metastability occurs when a digital circuit's flip-flop or latch is unable to resolve a signal within a clock cycle, leading to unpredictable output states, while a race condition happens when the order or timing of events causes unintended behavior in synchronous circuits. Understanding the subtle differences between metastability and race conditions will help you design more reliable digital systems, so explore the rest of the article to deepen your knowledge.

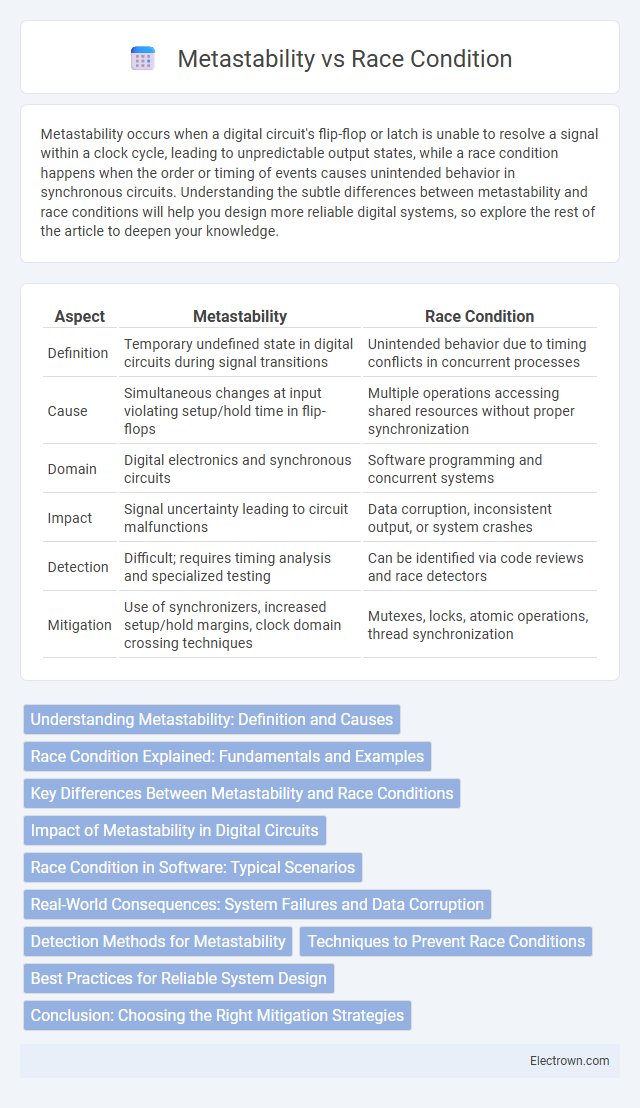

Table of Comparison

| Aspect | Metastability | Race Condition |

|---|---|---|

| Definition | Temporary undefined state in digital circuits during signal transitions | Unintended behavior due to timing conflicts in concurrent processes |

| Cause | Simultaneous changes at input violating setup/hold time in flip-flops | Multiple operations accessing shared resources without proper synchronization |

| Domain | Digital electronics and synchronous circuits | Software programming and concurrent systems |

| Impact | Signal uncertainty leading to circuit malfunctions | Data corruption, inconsistent output, or system crashes |

| Detection | Difficult; requires timing analysis and specialized testing | Can be identified via code reviews and race detectors |

| Mitigation | Use of synchronizers, increased setup/hold margins, clock domain crossing techniques | Mutexes, locks, atomic operations, thread synchronization |

Understanding Metastability: Definition and Causes

Metastability occurs when a digital circuit element, such as a flip-flop, fails to resolve to a stable logic level within the required time due to asynchronous input changes near its clock edge. This phenomenon is caused by timing violations where signals arrive too close to the sampling instant, leading to unpredictable intermediate voltage states. Understanding metastability is crucial for designing reliable synchronization circuits to prevent data corruption in digital systems.

Race Condition Explained: Fundamentals and Examples

Race conditions occur when multiple processes or threads access shared resources simultaneously without proper synchronization, leading to unpredictable outcomes or system errors. Metastability differs as it involves unstable intermediate states in digital circuits caused by asynchronous inputs, potentially resulting in timing violations and erroneous outputs. Understanding race conditions and their prevention through mechanisms like locks, semaphores, or atomic operations helps ensure your system's reliability and data integrity.

Key Differences Between Metastability and Race Conditions

Metastability occurs when a digital circuit fails to settle into a stable state within a clock cycle due to violating setup or hold times, resulting in unpredictable output. Race conditions arise when multiple signals simultaneously change, causing timing conflicts that produce incorrect or inconsistent circuit behavior. Understanding the key difference, metastability is related to timing violations causing uncertain outputs, whereas race conditions stem from competing signal paths creating timing hazards; your circuit design must carefully address both to ensure reliable performance.

Impact of Metastability in Digital Circuits

Metastability in digital circuits causes unpredictable voltage levels that can lead to erroneous data interpretation and system failures, especially in asynchronous signal synchronization. This condition can significantly degrade the reliability and timing performance of your sequential logic, resulting in data corruption or system instability. Designing robust circuits with proper synchronization techniques is essential to mitigate the impact of metastability and ensure stable digital operations.

Race Condition in Software: Typical Scenarios

Race condition in software occurs when two or more processes access shared resources concurrently, causing unpredictable behavior and erroneous outputs. Typical scenarios include multi-threaded applications modifying shared variables without proper synchronization and event-driven systems where timing of events leads to inconsistent states. Such vulnerabilities can result in data corruption, security breaches, or system crashes if not properly managed through locks, semaphores, or atomic operations.

Real-World Consequences: System Failures and Data Corruption

Metastability in digital circuits can cause unpredictable delays in signal transitions, leading to timing errors that compromise system reliability, while race conditions create a scenario where the system's behavior depends on the sequence or timing of uncontrollable events, resulting in timing conflicts and incorrect state transitions. Both metastability and race conditions can trigger system failures such as processor hangs, incorrect computations, and data corruption in memory or communication protocols. Effective mitigation techniques including synchronizers for metastability and atomic operations or proper locking mechanisms for race conditions are essential to maintain system integrity and prevent catastrophic operational issues.

Detection Methods for Metastability

Detection methods for metastability primarily involve using high-speed oscilloscopes and time-to-digital converters (TDCs) to monitor signal transitions and timing violations in digital circuits. Circuit designers employ metastability filters and resolution time measurements to identify instances where flip-flops fail to settle into a stable state, thus differentiating metastability from race conditions. Your designs benefit from integrating these detection tools to ensure reliable operation in asynchronous data transfers and clock domain crossings.

Techniques to Prevent Race Conditions

Techniques to prevent race conditions include implementing mutual exclusion mechanisms such as mutexes, semaphores, and critical sections, which ensure that only one process accesses shared resources at a time. Atomic operations and lock-free algorithms minimize the risk of concurrent access conflicts by guaranteeing indivisible updates to shared data. You can also employ hardware synchronization primitives and memory barriers to enforce proper ordering of memory operations and avoid unpredictable system behavior.

Best Practices for Reliable System Design

Metastability occurs when a signal fails to settle within the required time, causing unpredictable outputs, while race conditions arise from timing conflicts between signals or processes. Best practices for reliable system design include using synchronizers and avoiding asynchronous crossings to reduce metastability, and employing proper locking mechanisms, atomic operations, and well-defined critical sections to prevent race conditions. Designing for deterministic timing and thorough verification ensures heightened robustness in digital and concurrent systems.

Conclusion: Choosing the Right Mitigation Strategies

Effective mitigation of metastability involves synchronizer circuits that provide additional clock cycles for resolving uncertain states, while race conditions require careful timing analysis and the implementation of proper synchronization mechanisms such as mutexes or semaphores. Prioritizing metastability solutions is critical in high-speed digital systems where asynchronous inputs interact with clocked logic, whereas race condition strategies are essential in software and hardware designs handling concurrent processes. Selecting the right approach depends on system requirements and the nature of timing violations, combining design methodologies to ensure robust, predictable operation.

Metastability vs race condition Infographic

electrown.com

electrown.com