Propagation delay represents the time it takes for a signal to travel through a circuit component, while setup time defines the minimum period before the clock edge that data must be stable to ensure correct sampling. Understanding the difference between propagation delay and setup time is crucial for optimizing your digital system's timing performance--continue reading to learn how these parameters impact circuit reliability.

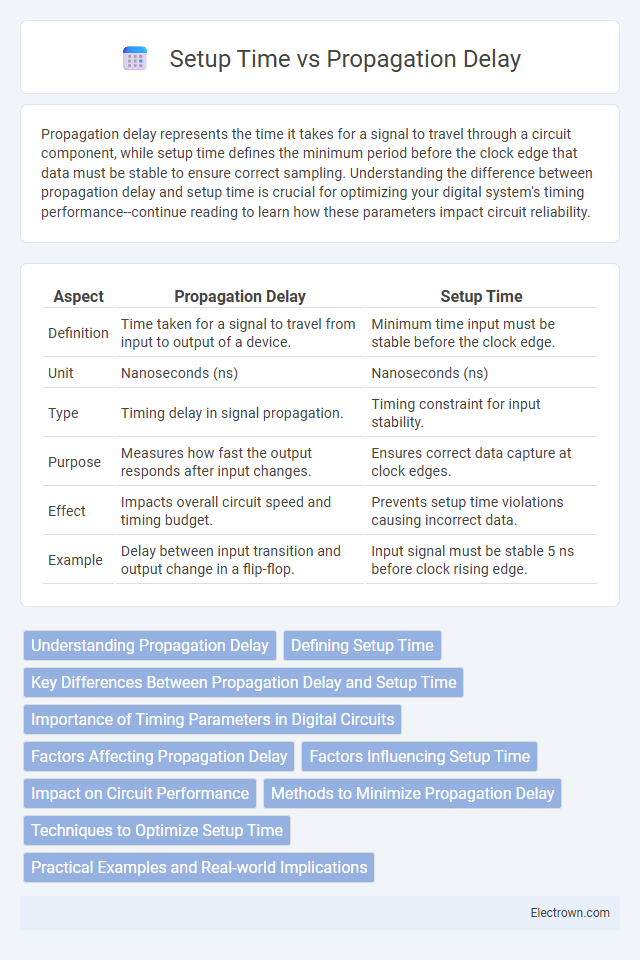

Table of Comparison

| Aspect | Propagation Delay | Setup Time |

|---|---|---|

| Definition | Time taken for a signal to travel from input to output of a device. | Minimum time input must be stable before the clock edge. |

| Unit | Nanoseconds (ns) | Nanoseconds (ns) |

| Type | Timing delay in signal propagation. | Timing constraint for input stability. |

| Purpose | Measures how fast the output responds after input changes. | Ensures correct data capture at clock edges. |

| Effect | Impacts overall circuit speed and timing budget. | Prevents setup time violations causing incorrect data. |

| Example | Delay between input transition and output change in a flip-flop. | Input signal must be stable 5 ns before clock rising edge. |

Understanding Propagation Delay

Propagation delay refers to the time interval required for a signal to travel from the input to the output of a digital circuit element, such as a flip-flop or logic gate. This delay directly impacts the maximum operating frequency of a circuit, as the output must be stable before the next clock edge triggers the setup time requirement. Accurately analyzing propagation delay is essential for timing analysis and ensuring reliable synchronous digital system performance.

Defining Setup Time

Setup time is the minimum interval before the clock edge during which the data input must remain stable to ensure proper latch or flip-flop operation. It is a critical timing parameter in digital circuits that defines the required data stabilization period preceding the clock transition. Accurate setup time analysis helps prevent data corruption and timing violations in synchronous systems, directly impacting the maximum achievable clock frequency.

Key Differences Between Propagation Delay and Setup Time

Propagation delay refers to the time taken for a signal to travel from the input to the output of a digital circuit, typically measured in nanoseconds. Setup time is the minimum duration before the clock edge during which the input signal must be stable to ensure correct data capture by a flip-flop or latch. The key difference lies in propagation delay being a measure of signal travel time, while setup time defines a timing constraint necessary for reliable data synchronization in sequential circuits.

Importance of Timing Parameters in Digital Circuits

Timing parameters such as propagation delay and setup time critically influence digital circuit performance by determining signal integrity and synchronization accuracy. Propagation delay impacts the speed at which data travels through logic gates, while setup time ensures data stability before the clock edge for reliable latch or flip-flop operation. Optimizing these parameters reduces timing violations and enhances circuit reliability in high-speed digital systems.

Factors Affecting Propagation Delay

Propagation delay is influenced by factors such as the physical length of the interconnects, the capacitance and resistance of the circuit components, and the operating temperature of the device. Process variations, supply voltage levels, and fan-out load also play critical roles in determining the total propagation delay in digital circuits. Understanding these parameters helps you optimize timing margins and improve overall circuit performance.

Factors Influencing Setup Time

Setup time is primarily influenced by process variation, temperature fluctuations, and supply voltage levels, which directly affect transistor switching characteristics. The complexity of the combinational logic before a register determines the required data stabilization period, impacting setup time. Signal integrity issues such as noise and crosstalk also play a crucial role in extending the necessary setup timing margin in synchronous circuits.

Impact on Circuit Performance

Propagation delay determines the speed at which signals travel through a circuit, directly impacting overall timing and data throughput. Setup time is crucial for ensuring data stability before the clock edge, preventing timing violations and data corruption. Your circuit performance improves when both propagation delay and setup time are minimized and balanced for optimal synchronization.

Methods to Minimize Propagation Delay

Minimizing propagation delay involves optimizing circuit design through techniques such as reducing gate capacitance, using faster transistor technologies like CMOS with low threshold voltages, and implementing pipelining to break down long logic paths. Adjusting transistor sizing and minimizing interconnect length also contribute to faster signal transitions, enhancing overall timing performance. Your digital system's speed can be significantly improved by carefully balancing these methods to reduce delays without compromising signal integrity or power consumption.

Techniques to Optimize Setup Time

Techniques to optimize setup time include using faster flip-flops with reduced metastability, minimizing logic depth in the data path to decrease propagation delays, and employing clock skew management to align data arrival with clock edges precisely. You can also implement pipeline stages to break down critical paths and balance timing requirements across registers. Advanced synthesis tools optimize timing by retiming and logic restructuring to ensure data meets setup constraints efficiently.

Practical Examples and Real-world Implications

Propagation delay, the time taken for a signal to travel through a circuit, directly impacts the timing margin available before the setup time, which is the minimum period a data input must remain stable before the clock edge. In high-speed digital systems like microprocessors and FPGAs, excessive propagation delay can cause data to arrive too late, violating setup time constraints and leading to timing errors or malfunction. Practical implications include the need for precise timing analysis and optimization in design tools to ensure reliable data transfer and system stability in real-world applications such as synchronous communication and clock domain crossings.

Propagation Delay vs Setup Time Infographic

electrown.com

electrown.com