Latch-up occurs when a parasitic structure in a semiconductor device causes a low-impedance path, leading to excessive current and potential device failure, while soft errors are transient faults caused by external radiation or electrical interference that temporarily disrupt data without damaging the hardware. Understanding the differences between latch-up and soft error is crucial for enhancing the reliability of your electronic systems--continue reading to explore their causes, detection methods, and prevention techniques.

Table of Comparison

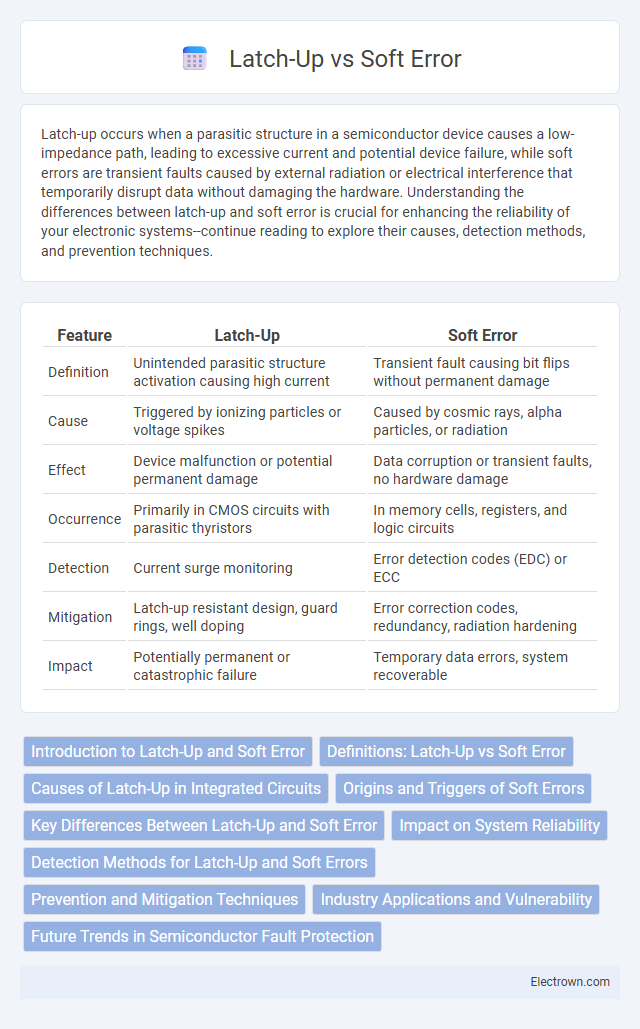

| Feature | Latch-Up | Soft Error |

|---|---|---|

| Definition | Unintended parasitic structure activation causing high current | Transient fault causing bit flips without permanent damage |

| Cause | Triggered by ionizing particles or voltage spikes | Caused by cosmic rays, alpha particles, or radiation |

| Effect | Device malfunction or potential permanent damage | Data corruption or transient faults, no hardware damage |

| Occurrence | Primarily in CMOS circuits with parasitic thyristors | In memory cells, registers, and logic circuits |

| Detection | Current surge monitoring | Error detection codes (EDC) or ECC |

| Mitigation | Latch-up resistant design, guard rings, well doping | Error correction codes, redundancy, radiation hardening |

| Impact | Potentially permanent or catastrophic failure | Temporary data errors, system recoverable |

Introduction to Latch-Up and Soft Error

Latch-up is a short-circuit condition in CMOS devices caused by parasitic structures triggering a low-impedance path, potentially leading to device failure if not mitigated. Soft errors occur when external radiation or cosmic rays induce transient faults in semiconductor memory or logic circuits, causing data corruption without permanent damage. Understanding these distinct failure mechanisms helps you design more robust integrated circuits by implementing targeted prevention and correction strategies.

Definitions: Latch-Up vs Soft Error

Latch-up is a short-circuit condition in CMOS circuits caused by parasitic thyristor structures, leading to high current flow and potential device damage. Soft error refers to transient faults in semiconductor devices caused by ionizing radiation or electromagnetic interference, resulting in temporary data corruption without permanent hardware damage. Both phenomena impact integrated circuit reliability but differ fundamentally in origin and effect.

Causes of Latch-Up in Integrated Circuits

Latch-up in integrated circuits is primarily caused by parasitic silicon-controlled rectifier (SCR) structures formed within the CMOS substrate, triggered by transient voltage spikes, overvoltage conditions, or ionizing radiation. It results from the inadvertent triggering of a low-impedance path between the power supply and ground, leading to high current flow and potential device failure. Proper layout techniques, guard rings, and substrate doping are essential to prevent latch-up and ensure circuit reliability.

Origins and Triggers of Soft Errors

Soft errors originate primarily from cosmic rays and radioactive decay particles striking semiconductor materials, causing transient faults in memory cells or logic circuits. These events are triggered by high-energy neutrons, alpha particles, and other ionizing radiation that induce charge disturbances, leading to bit flips or temporary malfunctions. Unlike latch-up, which results from parasitic structures in CMOS devices, soft errors do not cause permanent damage but affect data integrity and system reliability.

Key Differences Between Latch-Up and Soft Error

Latch-up is a permanent failure mode caused by parasitic structures in CMOS circuits, resulting in a low-impedance path and potential device destruction, whereas soft error is a transient fault caused by particle strikes leading to bit flips without lasting damage. Latch-up requires hardware redesign or process changes for mitigation, while soft errors are typically managed through error detection and correction codes or redundancy techniques. The key difference lies in latch-up's irreversible impact on circuit integrity compared to the soft error's temporary data corruption.

Impact on System Reliability

Latch-up events cause permanent damage to integrated circuits by creating a low-impedance path that may lead to device failure, severely compromising system reliability. Soft errors, induced by transient radiation or noise, result in temporary data corruption without physical damage, affecting system performance but allowing recovery through error correction mechanisms. The distinction in persistence and severity makes latch-up a critical design concern for long-term reliability, while soft errors primarily challenge data integrity and fault tolerance.

Detection Methods for Latch-Up and Soft Errors

Latch-up detection methods primarily involve on-chip current sensors that monitor sudden spikes in current indicative of parasitic thyristor activation, enabling rapid shutdown to prevent device damage. Soft error detection relies on error-correcting codes (ECC) and built-in self-test (BIST) circuits that identify transient bit flips caused by radiation-induced charge disturbances in memory cells. Real-time monitoring and redundancy techniques enhance detection accuracy for both Latch-up and soft errors in integrated circuits.

Prevention and Mitigation Techniques

Latch-up prevention techniques primarily involve designing robust guard rings around sensitive CMOS circuits, optimizing substrate doping profiles, and implementing silicon-on-insulator (SOI) technology to reduce parasitic thyristor action. Soft error mitigation often includes error-correcting codes (ECC), redundancy schemes like triple modular redundancy (TMR), and radiation-hardened circuit designs to detect and correct transient faults caused by particle strikes. Both approaches benefit significantly from process-level improvements and circuit-level hardening strategies tailored to specific operational environments and device technologies.

Industry Applications and Vulnerability

Latch-up primarily impacts integrated circuits in automotive and aerospace industries due to its high risk of causing permanent device damage, while soft errors, often caused by cosmic rays or alpha particles, frequently affect data integrity in memory and logic circuits within data centers and consumer electronics. This vulnerability requires robust design techniques such as guard rings and error-correcting codes (ECC) to protect your systems from catastrophic failures and transient faults. Understanding these failure modes is crucial for selecting the right semiconductor devices and implementing adequate fault-tolerance in mission-critical applications.

Future Trends in Semiconductor Fault Protection

Future trends in semiconductor fault protection emphasize advanced latch-up prevention techniques using silicon-on-insulator (SOI) technology and improved substrate isolation to reduce parasitic device activation. Soft error mitigation leverages error-correcting codes (ECC), radiation-hardened designs, and adaptive voltage scaling to enhance reliability in increasingly smaller nodes. Your device's fault tolerance will benefit from integrating machine learning algorithms for real-time anomaly detection and correction in emerging semiconductor architectures.

Latch-Up vs Soft Error Infographic

electrown.com

electrown.com