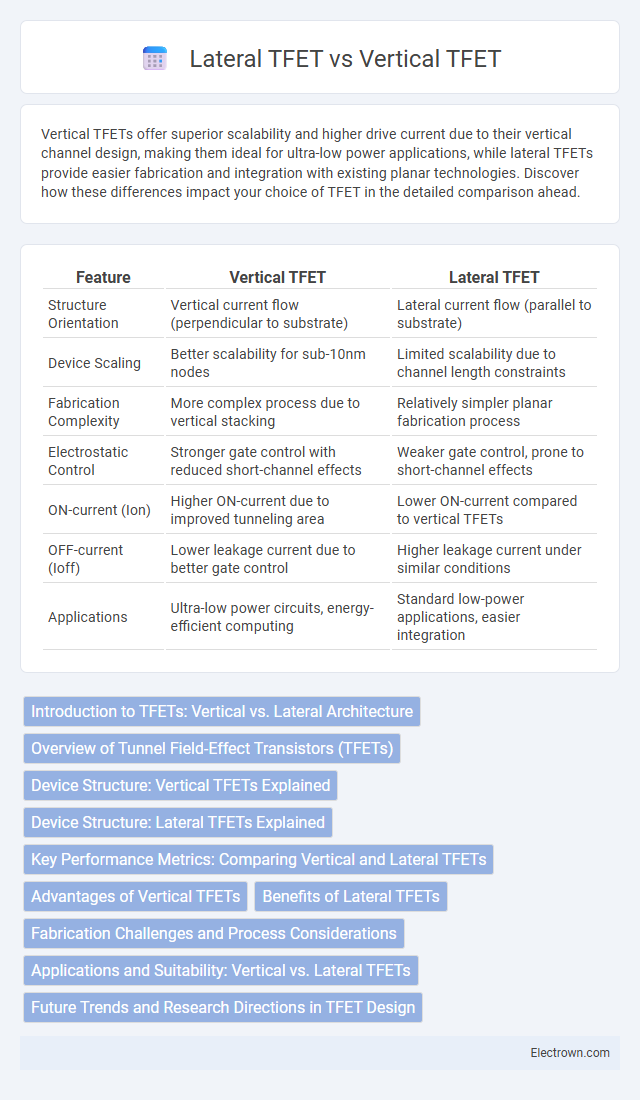

Vertical TFETs offer superior scalability and higher drive current due to their vertical channel design, making them ideal for ultra-low power applications, while lateral TFETs provide easier fabrication and integration with existing planar technologies. Discover how these differences impact your choice of TFET in the detailed comparison ahead.

Table of Comparison

| Feature | Vertical TFET | Lateral TFET |

|---|---|---|

| Structure Orientation | Vertical current flow (perpendicular to substrate) | Lateral current flow (parallel to substrate) |

| Device Scaling | Better scalability for sub-10nm nodes | Limited scalability due to channel length constraints |

| Fabrication Complexity | More complex process due to vertical stacking | Relatively simpler planar fabrication process |

| Electrostatic Control | Stronger gate control with reduced short-channel effects | Weaker gate control, prone to short-channel effects |

| ON-current (Ion) | Higher ON-current due to improved tunneling area | Lower ON-current compared to vertical TFETs |

| OFF-current (Ioff) | Lower leakage current due to better gate control | Higher leakage current under similar conditions |

| Applications | Ultra-low power circuits, energy-efficient computing | Standard low-power applications, easier integration |

Introduction to TFETs: Vertical vs. Lateral Architecture

Vertical TFETs feature a gate-all-around structure that enhances electrostatic control and reduces short-channel effects, making them suitable for ultra-scaled devices. Lateral TFETs, with their planar configuration, offer simpler fabrication and better integration with existing CMOS technology but often face challenges with tunneling efficiency and leakage current. The choice between vertical and lateral TFET architectures hinges on trade-offs in device performance, scalability, and manufacturing complexity.

Overview of Tunnel Field-Effect Transistors (TFETs)

Tunnel Field-Effect Transistors (TFETs) leverage quantum tunneling to achieve steep subthreshold slopes and ultra-low power consumption, distinguishing them from traditional MOSFETs. Vertical TFETs feature a channel oriented perpendicular to the substrate, enabling higher device density and improved electrostatic control, while lateral TFETs have a channel parallel to the substrate, offering simpler fabrication and integration with existing planar technologies. Advances in vertical TFET architectures focus on enhancing tunneling efficiency and scalability, critical for next-generation low-power electronics.

Device Structure: Vertical TFETs Explained

Vertical TFETs feature a device structure where the source, channel, and drain are stacked vertically, enabling a shorter tunneling path and improved electrostatic control compared to lateral TFETs. This vertical architecture allows for better scalability and higher drive currents by leveraging the current flow direction perpendicular to the substrate surface. Your choice between vertical and lateral TFETs will impact device performance, with vertical TFETs often providing enhanced switching efficiency and reduced short-channel effects.

Device Structure: Lateral TFETs Explained

Lateral TFETs feature a horizontal device architecture where the source, channel, and drain are aligned side-by-side on the same plane, enabling easier integration with existing CMOS technologies. This structure allows precise gate control over the tunneling junction, enhancing subthreshold swing and minimizing short-channel effects. The planar design of lateral TFETs supports scalable fabrication, making them suitable for low-power and high-speed applications in advanced semiconductor devices.

Key Performance Metrics: Comparing Vertical and Lateral TFETs

Vertical TFETs exhibit superior current drive capabilities with higher ON-current (I_ON) values due to their reduced channel length and enhanced electrostatic control, resulting in improved switching speeds. Lateral TFETs tend to have lower OFF-current (I_OFF) leakage, contributing to better energy efficiency at the expense of slower response times. The subthreshold swing (SS) in vertical TFETs is generally steeper, enabling faster transitions between ON and OFF states compared to lateral TFETs, which affects overall device performance in low-power applications.

Advantages of Vertical TFETs

Vertical Tunnel Field-Effect Transistors (TFETs) exhibit superior electrostatic control and scalability compared to lateral TFETs, resulting from their vertical channel architecture that minimizes short-channel effects. The vertical configuration enables higher drive current density and reduced device footprint, enhancing integration density for advanced semiconductor applications. Furthermore, Vertical TFETs facilitate efficient gate-to-channel coupling, improving subthreshold swing and energy efficiency in low-power electronics.

Benefits of Lateral TFETs

Lateral TFETs offer improved scalability and easier integration with existing planar CMOS fabrication processes, making them cost-effective for mass production. Their horizontal channel structure facilitates enhanced electrostatic control, leading to lower subthreshold swing and reduced leakage current. You gain better device performance in low-power applications due to the efficient gate control and compact layout of lateral TFETs.

Fabrication Challenges and Process Considerations

Vertical TFETs face significant fabrication challenges due to their complex 3D structures, requiring advanced epitaxial growth and precise alignment of gate and source/drain regions to ensure optimal tunneling performance. Lateral TFETs, while easier to integrate with existing planar CMOS processes, struggle with scaling and achieving high drive currents due to increased channel length and variability in doping profiles. Your choice between vertical and lateral TFETs should consider process compatibility, yield, and the trade-offs between device scalability and fabrication complexity.

Applications and Suitability: Vertical vs. Lateral TFETs

Vertical TFETs are ideal for high-density integration in low-power applications such as IoT devices and energy-efficient processors due to their superior electrostatic control and reduced short-channel effects. Lateral TFETs suit flexible electronics and sensors where planar device geometry provides easier fabrication and integration with existing CMOS technologies. The choice between vertical and lateral TFETs depends on application-specific requirements like power consumption, device scaling, and fabrication complexity.

Future Trends and Research Directions in TFET Design

Vertical TFETs show promise in enhancing gate control and scaling potential, making them a focal point for future research targeting ultra-low power applications and high-density integration. Lateral TFETs remain important for compatibility with existing CMOS processes while ongoing studies emphasize material engineering and interface optimization to boost performance metrics such as ON-current and subthreshold slope. Emerging trends include hybrid device architectures and advanced simulation techniques to overcome tunneling bottlenecks and achieve energy-efficient nanoelectronic systems.

Vertical TFET vs Lateral TFET Infographic

electrown.com

electrown.com