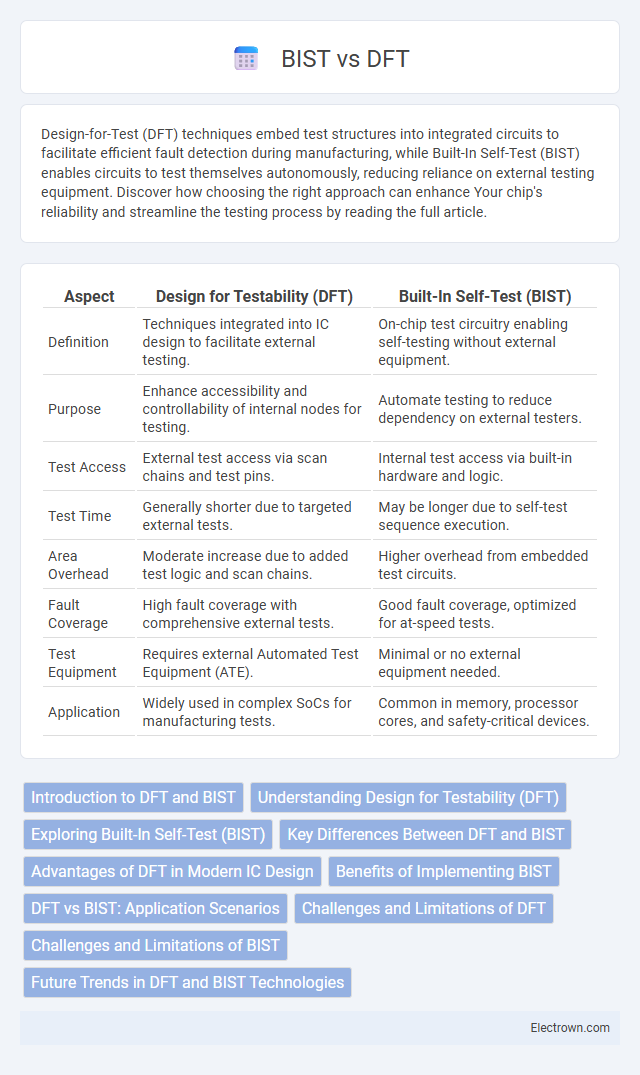

Design-for-Test (DFT) techniques embed test structures into integrated circuits to facilitate efficient fault detection during manufacturing, while Built-In Self-Test (BIST) enables circuits to test themselves autonomously, reducing reliance on external testing equipment. Discover how choosing the right approach can enhance Your chip's reliability and streamline the testing process by reading the full article.

Table of Comparison

| Aspect | Design for Testability (DFT) | Built-In Self-Test (BIST) |

|---|---|---|

| Definition | Techniques integrated into IC design to facilitate external testing. | On-chip test circuitry enabling self-testing without external equipment. |

| Purpose | Enhance accessibility and controllability of internal nodes for testing. | Automate testing to reduce dependency on external testers. |

| Test Access | External test access via scan chains and test pins. | Internal test access via built-in hardware and logic. |

| Test Time | Generally shorter due to targeted external tests. | May be longer due to self-test sequence execution. |

| Area Overhead | Moderate increase due to added test logic and scan chains. | Higher overhead from embedded test circuits. |

| Fault Coverage | High fault coverage with comprehensive external tests. | Good fault coverage, optimized for at-speed tests. |

| Test Equipment | Requires external Automated Test Equipment (ATE). | Minimal or no external equipment needed. |

| Application | Widely used in complex SoCs for manufacturing tests. | Common in memory, processor cores, and safety-critical devices. |

Introduction to DFT and BIST

Design for Testability (DFT) integrates specific features into integrated circuits to simplify testing and improve fault detection during manufacturing. Built-In Self-Test (BIST) is a DFT technique where test logic is embedded within the chip, enabling autonomous testing without external equipment. Your choice between DFT and BIST depends on factors like test coverage, cost, and system complexity.

Understanding Design for Testability (DFT)

Design for Testability (DFT) integrates specialized techniques and structures within integrated circuits to improve fault detection, enabling more efficient and accurate testing processes. By incorporating test points, scan chains, and built-in test logic, DFT facilitates easier fault isolation and increases test coverage without significantly impacting chip performance. This approach reduces overall manufacturing costs and enhances product reliability through streamlined testing and diagnostics.

Exploring Built-In Self-Test (BIST)

Built-In Self-Test (BIST) is an advanced design-for-testability (DFT) technique that enables integrated circuits to test themselves autonomously, improving fault detection and reducing dependency on external testing equipment. BIST embeds test pattern generation, output response analysis, and diagnostic features within the chip, which significantly shortens test time and lowers manufacturing costs. The approach is particularly effective in complex system-on-chip (SoC) architectures where traditional DFT methods struggle with scalability and test coverage.

Key Differences Between DFT and BIST

Design for Testability (DFT) integrates specific test structures and access points into integrated circuits to facilitate external testing processes, while Built-In Self-Test (BIST) embeds self-testing mechanisms within the chip, enabling autonomous fault detection without external equipment. DFT relies heavily on external Automatic Test Equipment (ATE) for test pattern generation and result analysis, whereas BIST generates test patterns internally and interprets responses on-chip, reducing dependence on external testers. The primary difference lies in test application approach: DFT enhances accessibility for external testing, while BIST implements self-contained test execution, improving test speed and on-field diagnostics.

Advantages of DFT in Modern IC Design

Design for Testability (DFT) enhances modern IC design by enabling easier identification and diagnosis of manufacturing defects, significantly improving test coverage and fault isolation. Incorporating DFT techniques reduces time-to-market and lowers production costs through automated testing and minimized reliance on external test equipment. Your chip's reliability and yield improve as DFT supports built-in scan chains and boundary-scan methods that streamline in-field testing and debugging.

Benefits of Implementing BIST

Built-In Self-Test (BIST) enhances your testing process by enabling on-chip fault detection, reducing reliance on external testing equipment and lowering overall test costs. Implementing BIST improves test coverage and speeds up the diagnosis of faults during manufacturing and field operation. This integration supports higher reliability and shorter time-to-market compared to traditional Design for Testability (DFT) methods.

DFT vs BIST: Application Scenarios

Design for Testability (DFT) is primarily applied during the integrated circuit manufacturing process to facilitate efficient fault detection and enhance test coverage through built-in test points and scan chains. Built-In Self-Test (BIST) is mainly used in-field and production environments for autonomous testing of circuits without external test equipment, enabling quick diagnostics and reliability verification. DFT suits early-stage design verification and manufacturing tests, while BIST excels in on-chip self-testing and periodic maintenance in deployed systems.

Challenges and Limitations of DFT

Design for Testability (DFT) faces challenges such as increased silicon area overhead and potential performance degradation due to additional test circuitry. Complex test pattern generation and the need for enhanced test access mechanisms can limit its effectiveness in detecting all fault types. Your design may also suffer from longer test times and higher costs compared to Built-In Self-Test (BIST) approaches, which integrate test functions internally to address some of these limitations.

Challenges and Limitations of BIST

Built-In Self-Test (BIST) faces challenges such as increased chip area due to additional test circuitry, which can impact design cost and power consumption. The complexity of integrating BIST can lead to limitations in fault coverage, especially for detecting subtle or rare defects within your system. Moreover, designing efficient BIST algorithms that minimize test time without compromising accuracy remains a significant constraint.

Future Trends in DFT and BIST Technologies

Future trends in Design for Testability (DFT) and Built-In Self-Test (BIST) technologies emphasize increased integration of AI-driven diagnostic tools and adaptive testing algorithms to enhance fault coverage and reduce test time. Emerging semiconductor processes demand scalable and low-power test solutions, pushing advancements in BIST architectures that support real-time, in-field testing for complex system-on-chip (SoC) designs. Your testing strategies will benefit from these innovations by achieving higher reliability and cost-effectiveness in next-generation electronic devices.

DFT vs BIST Infographic

electrown.com

electrown.com