LVDS offers high-speed data transmission with low power consumption, making it ideal for high-frequency applications, while CMOS logic provides versatile digital circuit functionality with lower noise margins and power efficiency. Explore the detailed comparison to understand which technology best suits your design requirements.

Table of Comparison

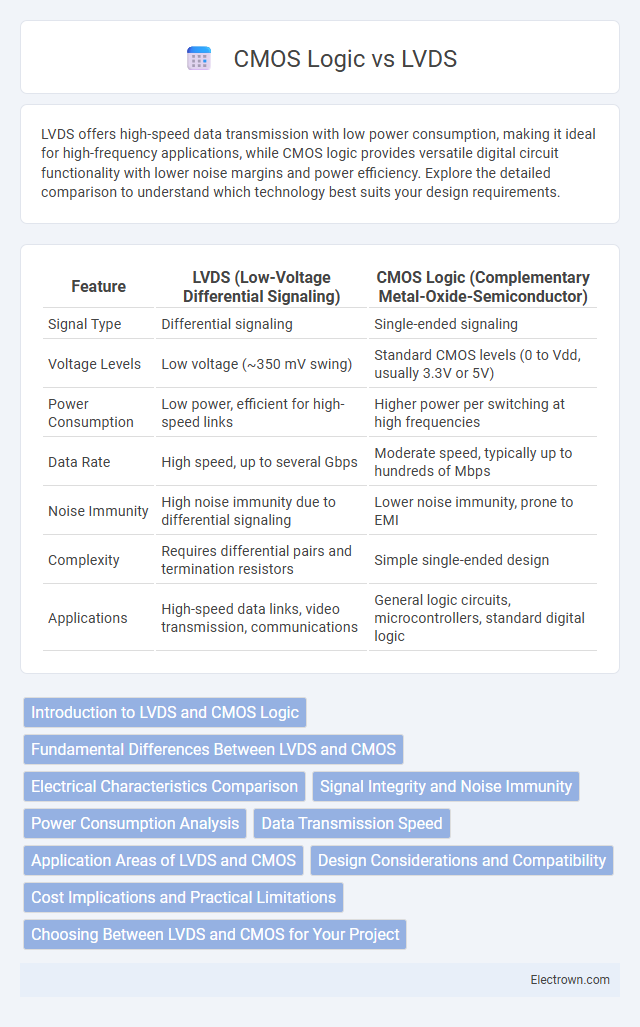

| Feature | LVDS (Low-Voltage Differential Signaling) | CMOS Logic (Complementary Metal-Oxide-Semiconductor) |

|---|---|---|

| Signal Type | Differential signaling | Single-ended signaling |

| Voltage Levels | Low voltage (~350 mV swing) | Standard CMOS levels (0 to Vdd, usually 3.3V or 5V) |

| Power Consumption | Low power, efficient for high-speed links | Higher power per switching at high frequencies |

| Data Rate | High speed, up to several Gbps | Moderate speed, typically up to hundreds of Mbps |

| Noise Immunity | High noise immunity due to differential signaling | Lower noise immunity, prone to EMI |

| Complexity | Requires differential pairs and termination resistors | Simple single-ended design |

| Applications | High-speed data links, video transmission, communications | General logic circuits, microcontrollers, standard digital logic |

Introduction to LVDS and CMOS Logic

LVDS (Low-Voltage Differential Signaling) employs differential signaling to achieve high-speed data transmission with low power consumption and reduced electromagnetic interference, making it ideal for high-frequency communication interfaces. CMOS (Complementary Metal-Oxide-Semiconductor) logic utilizes complementary p-type and n-type MOSFETs to implement integrated circuits with low static power dissipation, widely adopted in digital logic design for microprocessors and memory devices. The fundamental difference lies in LVDS's differential signals optimized for speed and noise immunity, whereas CMOS logic operates with single-ended voltage levels emphasizing energy efficiency and integration density.

Fundamental Differences Between LVDS and CMOS

LVDS (Low-Voltage Differential Signaling) and CMOS (Complementary Metal-Oxide-Semiconductor) logic differ fundamentally in their signaling methods and power consumption. LVDS uses differential signaling with a constant low voltage swing, enabling high-speed data transmission with minimal electromagnetic interference and low power usage. In contrast, CMOS logic relies on single-ended voltage levels for switching, typically consuming more power and being slower at high frequencies compared to LVDS.

Electrical Characteristics Comparison

LVDS (Low Voltage Differential Signaling) features low voltage swing of about 350 mV and differential signaling, resulting in high noise immunity and low electromagnetic interference, ideal for high-speed data transmission. CMOS logic levels typically operate with rail-to-rail voltage swings (0 V to Vdd, often 3.3 V or 5 V), consuming less static power but being more susceptible to noise and generating higher electromagnetic emissions. LVDS offers faster switching speeds and lower power consumption per bit compared to CMOS, making it preferable for high-frequency, noise-sensitive applications.

Signal Integrity and Noise Immunity

LVDS offers superior signal integrity compared to CMOS logic due to its low voltage swing and differential signaling, which minimizes electromagnetic interference and crosstalk. CMOS logic, relying on single-ended signals, is more susceptible to noise and signal degradation in high-speed or electrically noisy environments. The differential nature of LVDS enhances noise immunity, making it ideal for high-speed data transmission in demanding industrial and communication applications.

Power Consumption Analysis

LVDS (Low-Voltage Differential Signaling) consumes significantly less power compared to CMOS logic due to its low voltage swing and differential signaling technique, which minimizes current flow during switching. CMOS logic, while efficient for static power consumption, often exhibits higher dynamic power usage because of larger voltage swings and capacitive charging in digital circuits. LVDS's reduced power consumption makes it ideal for high-speed data transmission applications where energy efficiency is critical.

Data Transmission Speed

LVDS (Low-Voltage Differential Signaling) offers significantly higher data transmission speeds compared to CMOS (Complementary Metal-Oxide-Semiconductor) logic due to its low voltage swing and differential signaling, which reduce noise and signal degradation. While CMOS logic is typically limited to slower data rates for general-purpose applications, LVDS can achieve multi-gigabit per second speeds, making it ideal for high-speed communication interfaces. Your choice between these technologies should consider LVDS for demanding high-speed data transfer requirements.

Application Areas of LVDS and CMOS

LVDS (Low-Voltage Differential Signaling) is predominantly used in high-speed data transmission applications such as display interfaces, telecommunications, and high-performance computing due to its low power consumption and noise immunity. CMOS logic finds broad application in digital integrated circuits including microprocessors, memory devices, and various embedded systems, owing to its low static power dissipation and high noise margin. Both technologies serve distinct roles in electronics, with LVDS excelling in communication and signal integrity, while CMOS dominates general-purpose digital logic and low-power applications.

Design Considerations and Compatibility

LVDS and CMOS logic differ significantly in design considerations, particularly in power consumption and signal integrity; LVDS offers low power and high-speed differential signaling suitable for long-distance transmission, whereas CMOS logic is simpler and consumes more power but is widely compatible with various digital circuits. Compatibility between LVDS and CMOS requires careful level shifting and termination to match voltage levels and impedances, ensuring reliable data transfer without signal degradation. Your design must address these factors to balance speed, power efficiency, and interoperability in mixed-signal systems.

Cost Implications and Practical Limitations

LVDS (Low-Voltage Differential Signaling) typically incurs higher costs due to its complex circuitry and need for specialized components, making it less ideal for budget-sensitive projects compared to CMOS logic, which benefits from widespread manufacturing and lower material expenses. CMOS logic offers simpler design and integration advantages with low static power consumption, but faces speed and noise immunity limitations in high-frequency or long-distance signaling applications. LVDS provides superior noise resistance and faster data rates, yet demands careful PCB design and higher power consumption, constraining its use in cost-sensitive or low-power environments.

Choosing Between LVDS and CMOS for Your Project

Choosing between LVDS and CMOS logic depends on your project's speed, power consumption, and noise immunity requirements. LVDS offers high-speed data transmission with low power and excellent noise resistance, ideal for long-distance or high-frequency applications. CMOS logic suits low-speed, low-power circuits with simpler designs, making it cost-effective for general purpose use.

LVDS vs CMOS Logic Infographic

electrown.com

electrown.com