Package on package (PoP) stacking enhances electronic device miniaturization by vertically integrating memory and logic chips, improving performance and reducing signal delay. Explore the rest of the article to understand how this technology compares with package in package (PiP) designs and determine which solution best fits your advanced electronic needs.

Table of Comparison

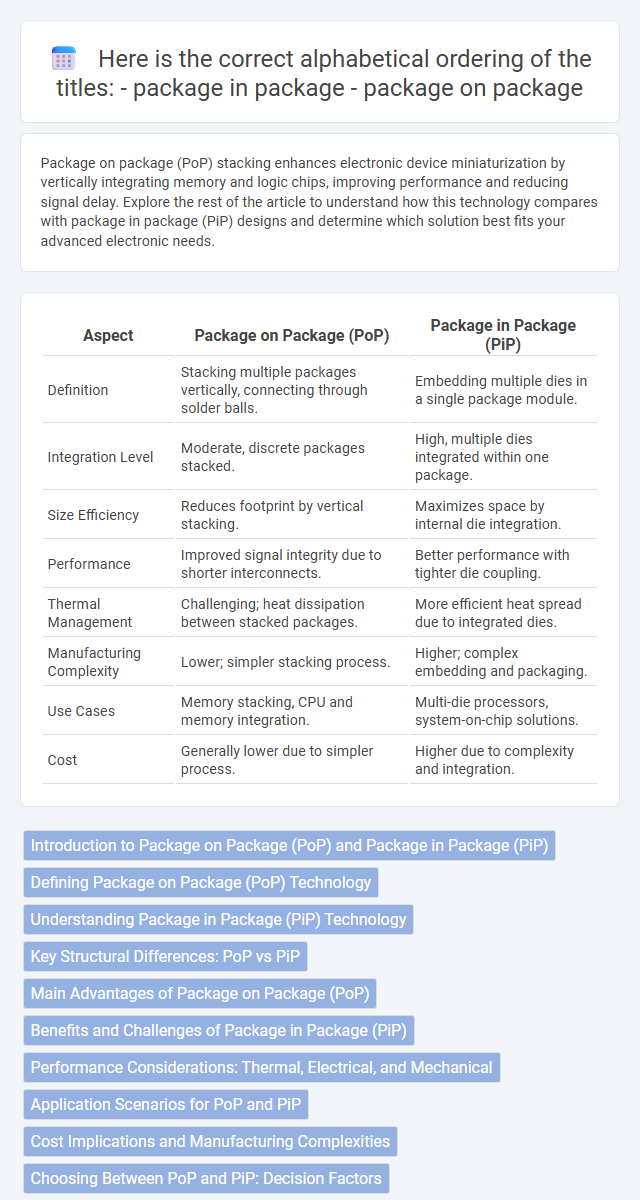

| Aspect | Package on Package (PoP) | Package in Package (PiP) |

|---|---|---|

| Definition | Stacking multiple packages vertically, connecting through solder balls. | Embedding multiple dies in a single package module. |

| Integration Level | Moderate, discrete packages stacked. | High, multiple dies integrated within one package. |

| Size Efficiency | Reduces footprint by vertical stacking. | Maximizes space by internal die integration. |

| Performance | Improved signal integrity due to shorter interconnects. | Better performance with tighter die coupling. |

| Thermal Management | Challenging; heat dissipation between stacked packages. | More efficient heat spread due to integrated dies. |

| Manufacturing Complexity | Lower; simpler stacking process. | Higher; complex embedding and packaging. |

| Use Cases | Memory stacking, CPU and memory integration. | Multi-die processors, system-on-chip solutions. |

| Cost | Generally lower due to simpler process. | Higher due to complexity and integration. |

Introduction to Package on Package (PoP) and Package in Package (PiP)

Package on Package (PoP) technology stacks multiple integrated circuits vertically to enhance device performance and save PCB space, commonly used in mobile devices and compact electronics. Package in Package (PiP) encloses two or more integrated circuits within a single package, offering improved signal integrity and thermal management for complex applications. Understanding the differences between PoP and PiP helps you choose the optimal packaging solution based on your device's size, performance, and manufacturing requirements.

Defining Package on Package (PoP) Technology

Package on Package (PoP) technology involves stacking multiple integrated circuit packages vertically to enhance functionality and save space on printed circuit boards. PoP enables high-density memory integration by placing memory chips directly atop a processor, improving data transfer speeds through shorter interconnects. This method differs from Package in Package (PiP), which embeds multiple dies within a single package, whereas PoP stacks separate packages.

Understanding Package in Package (PiP) Technology

Package in Package (PiP) technology integrates multiple ICs vertically within a single package, enhancing performance by reducing signal path lengths and saving PCB space. Unlike Package on Package (PoP), which stacks separate packages, PiP embeds chips inside one package, allowing for better thermal management and improved electrical characteristics. Your device benefits from PiP through increased functionality and miniaturization, critical in modern compact electronics.

Key Structural Differences: PoP vs PiP

Package on Package (PoP) stacks two or more integrated circuit packages vertically, connecting them through solder balls to save PCB space while allowing separate manufacturing of logic and memory chips. Package in Package (PiP) integrates multiple dies within a single package enclosure, offering a more compact and tightly integrated solution with direct die-to-die communication. Understanding these key structural differences helps optimize Your design for space efficiency or performance requirements.

Main Advantages of Package on Package (PoP)

Package on Package (PoP) technology offers significant advantages including enhanced vertical integration, which leads to reduced overall footprint on the PCB and improved signal integrity by minimizing interconnect lengths. PoP allows for independent testing of each package, increasing manufacturing yield and flexibility in component selection. This stacking method also facilitates heterogeneous integration, enabling combinations of logic and memory chips with optimized thermal management compared to Package in Package (PiP) solutions.

Benefits and Challenges of Package in Package (PiP)

Package in Package (PiP) technology offers significant benefits such as enhanced component integration, reduced footprint, and improved electrical performance by stacking multiple dies vertically within a single package. The challenges primarily involve complex thermal management, higher manufacturing costs, and design intricacies related to die stacking and interconnect reliability. Despite these issues, PiP enables advanced miniaturization and performance improvements ideal for high-density applications like smartphones and IoT devices.

Performance Considerations: Thermal, Electrical, and Mechanical

Package on Package (PoP) offers superior electrical performance by minimizing parasitic inductance and resistance through direct stacking of components, enhancing signal integrity and reducing latency. Thermal management can be challenging in PoP due to heat dissipation between stacked layers, requiring careful design to prevent overheating and ensure reliability. Package in Package (PiP) provides better thermal performance by integrating components within a single package substrate, offering improved mechanical stability and efficient heat spreading, which benefits devices with stringent thermal and mechanical requirements.

Application Scenarios for PoP and PiP

Package on Package (PoP) is ideal for enhancing memory capacity in mobile devices by stacking memory chips directly on top of the processor, optimizing space and performance for smartphones and tablets. Package in Package (PiP) suits applications requiring heterogeneous integration, such as combining analog and digital components in compact IoT devices or advanced RF modules. Your choice between PoP and PiP depends on specific needs like space constraints, thermal management, and electrical performance.

Cost Implications and Manufacturing Complexities

Package on Package (PoP) technology generally incurs higher manufacturing complexities due to the need for precise vertical alignment and interconnects between stacked components, impacting production yields and assembly time. Package in Package (PiP) offers cost advantages by integrating multiple dies within a single molded package, reducing board space and simplifying supply chain logistics, though it demands sophisticated design to manage thermal and signal integrity challenges. Understanding these trade-offs helps you optimize your product design for both cost efficiency and manufacturing feasibility.

Choosing Between PoP and PiP: Decision Factors

Choosing between Package on Package (PoP) and Package in Package (PiP) depends on your device's space constraints, thermal management needs, and electrical performance requirements. PoP stacks memory chips directly on top of a processor, optimizing vertical space and simplifying PCB design, making it ideal for compact mobile devices. PiP integrates multiple ICs within a single package, enhancing signal integrity and reducing latency, which benefits high-performance applications demanding robust interconnections.

package on package vs package in package Infographic

electrown.com

electrown.com